## Dual Address Space & <u>Dual Address Space</u>

Dan Greiner dgreiner@us.ibm.com z/Server Architecture SHARE 118 in Atlanta

Session 10446, 12 March 2012, 4:30 pm

IBM Systems and Technology Group (STG)

Copyright International Business Machines Corporation 2012

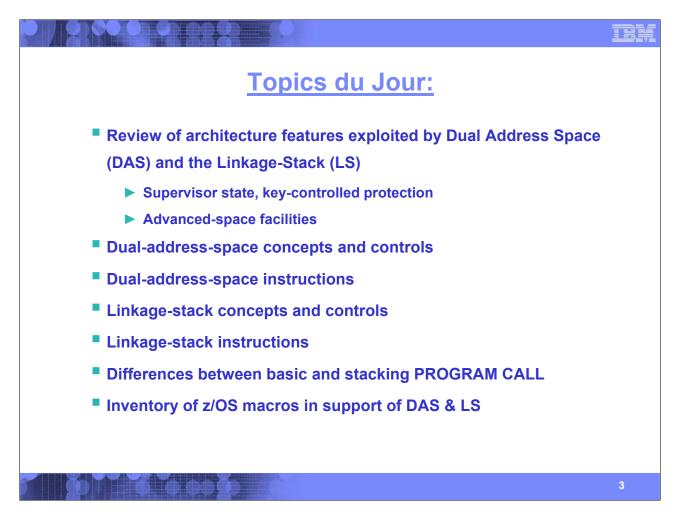

This presentation discusses two extremely powerful features of z/Architecture: the dual-address-space facility and the linkage stack.

I was interested in pursuing this topic for several years, and recently several factors influenced me to finally craft a presentation: (a) An associate from a past SHARE asked if I had such a topic, (b) a previous SHARE presentation by Kristine Harper discussed crossmemory communication, but did not delve into the hardware, (c) a colleague in my department wanted more information on the topic, and (d) Dr. John Ehrman (head of the SHARE Assembler Project) was looking for new content for SHARE 118 in Atlanta. How could I refuse?

This presentation is done as a part of the SHARE Assembler Project, which is well known for its "Assembler University" sessions including the popular Assembler Boot Camp (ABC). Using the university analogy where the ABC sessions represent entry-level undergraduate training, this session represents post-graduate-level material that is rather arcane. However, if you have the patience to muddle through this presentation (a) give yourself a pat on the back for perseverance, and (b) you will have an expert-level understanding of one of the features that distinguishes System z from other platforms. Note, for the purposes of brevity, this presentation does not provide all of the details of the operation of these features. For a complete understanding of this architecture, please refer to the z/Architecture Principles of Operation (SA22-7832).

In previous SHARE conferences, I have presented a topic on dynamic address translation (DAT) and access-register translation (ART). These topics are very closely related to the concept of the dual-address-space facility, and may be useful prerequisite reading.

This presentation was developed using PowerPoint, and makes extensive use of animation to illustrate the concepts (and, during a live presentation, to keep your eyes on the screen rather than your laptop). In these notes, the text **[CLICK]** indicates an advancement to the next animation on a slide.

Note, when submitted to the SHARE web site, the presentation is converted to a PDF, thus all of the animation is lost. If you would like a copy of the PowerPoint file, please see me after the session, or send me an e-mail to the address on the first slide.

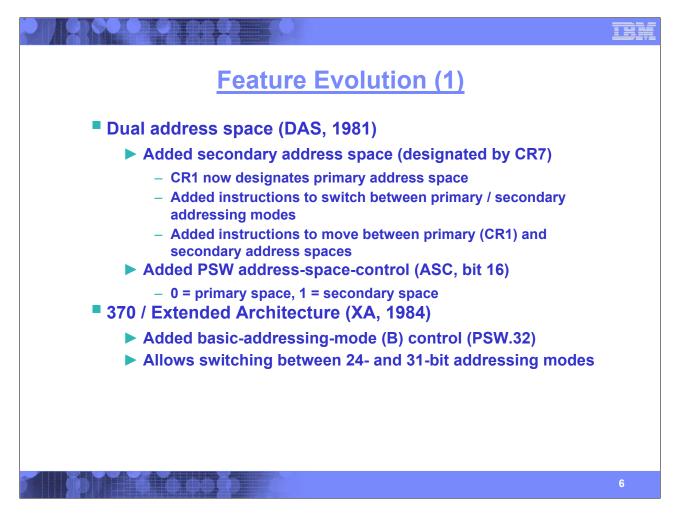

This slide is self explanatory.

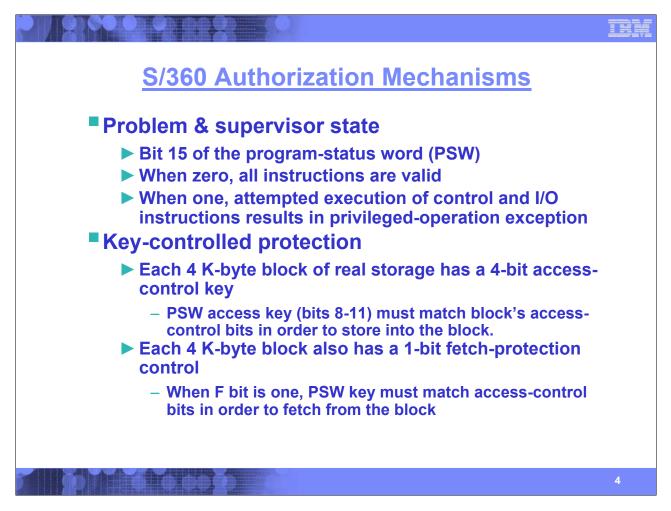

Nearly 50 years ago, IBM introduced the System 360 series of processors. This slide highlights two of the architectural features that contributed to the ongoing reliability of the S/360 and its follow-on systems.

The problem-state bit, bit 15 of the program-status word (PSW), when zero, allows the execution of control instructions that are normally restricted to use by an operating system. Bit 15 is normally one for the execution of most application programs – except when such programs invoke system services that are provided by the operating system. Restricting the execution of control instructions prevents unauthorized programs from manipulating key areas of the system, thus improving system reliability.

The storage-protection key is a feature that has contributed significantly to improved system reliability, by allowing the segregation of storage into 16 separate classifications. Originally, the storage-protection key was only four access-control bits per 4 K-byte block. When the key in the PSW was nonzero, the key in the PSW had to match the access-control bits in for the block in order to store into the block. Similarly, a key was specified during the execution of a channel program which, when nonzero, had to match the access-control bits in order to store into a block.

Subsequently, a fetch-protection bit was added to the key for each block; when the PSW (or channel) key was nonzero, and the fetchprotection bit was one in a block's key, a match of the PSW (or channel) key and the access-control bits for a block was required in order to fetch from the block. When the PSW (or channel) key was zero, key-controlled checking was not performed for storage accesses.

With the advent of dynamic address translation in the S/370, a reference and change bit were added to the key. The reference bit is set to one whenever a block of storage is referenced, and the change bit is set to one whenever a block is changed. These features are used by an operating system's virtual and real storage-management components to determine which blocks need to be migrated to auxiliary storage before reassigned.

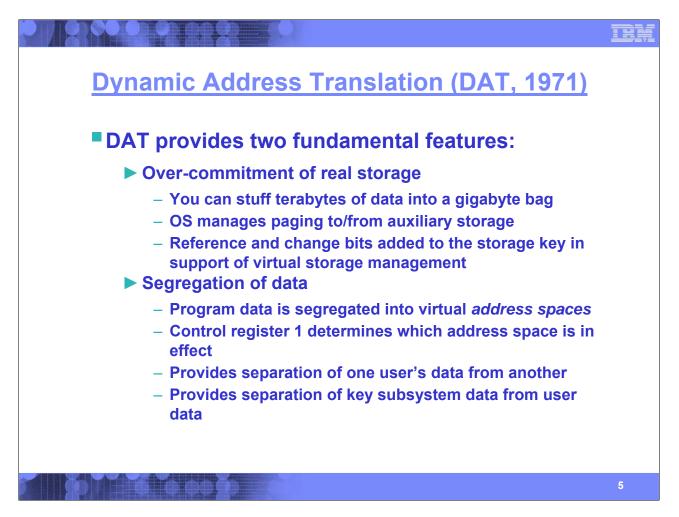

When dynamic address translation (DAT) was first introduced in the S/370, central storage was a precious commodity. DAT, in conjunction with paging by the operating system, provided the means by which a real storage could be over-commited, giving the illusion of having much more virtual storage than was actually installed in the machine.

However, another of the characteristics of DAT is perhaps more important – the ability to segregate data. This segregation can take the form of major subsystem components, or it may simply apply to keeping one user's data apart from another's. The S/360 architecture provided 16 storage keys for segregating data; DAT provides a much broader scope of segregation ... literally thousands of address spaces can be managed.

Understanding this function of DAT – that is, the segregation of programs and data – is a key prerequisite for understanding the power of the dual-address-space functions described herein. Session 8192 from the San Jose SHARE in 2008 provides background information on DAT: http://proceedings.share.org/proceedings/

A powerful characteristic of DAT is the "D" in its acronym: it is dynamic. Control register 1 (CR1) contains a pointer to a set of translation tables used by the hardware to map virtual memory into real memory. With a single instruction, the operating system can reload CR1 to designate an entirely different virtual context ... a different subsystem or user ... or in the VM environment, a different virtual machine.

The dual-address-space facility was added to the S/370 architecture in 1981. Whereas DAT originally provided a single translation-table origin, DAS now provides a primary and a secondary set of translation tables. For example, a primary address space representing a user's program may be designated by CR1, while a secondary address space representing an OS service needed by the user may be designated by CR7. Thus, two address spaces – primary and secondary -- are provided.

A series of new instructions provided the means by which a program could move data between the primary and secondary address spaces. Addition instructions allowed the program to query the primary and secondary address-space numbers (ASNs), call programs in other address spaces in a highly structured manner similar to supervisor calls, but not necessarily going into supervisor state.

A user-settable control in the PSW, called the address-space control (ASC) provided the means by which programs could switch between primary and secondary addressing for storage operands. As would be expected, there were certain authorization requirements in order to utilize such instructions.

Note, anyone who is familiar with access-register translation (ART) will likely say, "So what? I can have sixteen address spaces available at once, and I can change them at will."

Agreed, however, even with AR mode, the ability to call programs in other address spaces, with increasing or decreasing authority is one of the features that continues to be a DAS exclusive.

As the architecture grew, the program now had control over the addressing mode: either 24- or 31-bit addressing was provided, selectable by a program-controlled bit in the PSW. This bit, originally called the A-mode bit, is now (as of z/Architecture) called the basic-addressing-mode bit (B). This control is one that is managed by the DAS functions.

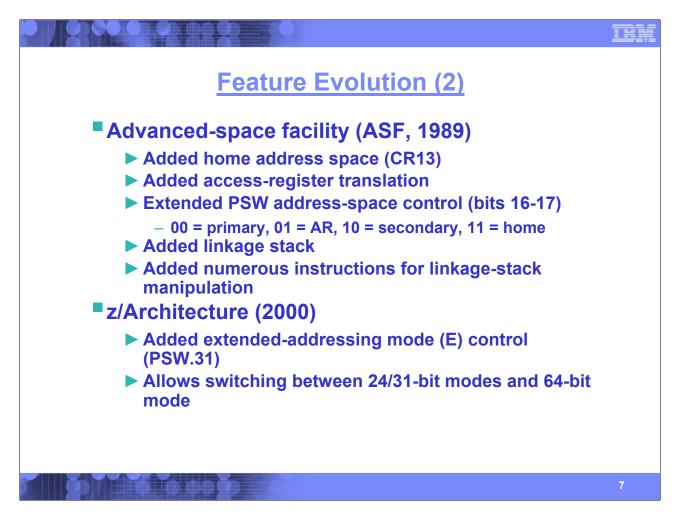

As noted on the previous slide, there's this thing called AR mode. Introduced in 1989, the advanced-space facility (ASF) included AR mode, and the home address space mode. The PSW's address-space control was extended to allow user selection of primary, secondary, AR-specified, or home address space modes.

The ASF also introduced a few new concepts: a dispatchable unit of work (more commonly known in MVS parlance as a task). The home address space represents the initial address space of the task, the space in which the task's control blocks exist, and, if the task has called multiple other address spaces, the space that gets the blame (i.e., abended) should the task encounter an unrecovered error.

ASF also introduced a linkage stack. This is a push-down stack that can be used by authorized and nonauthorized programs alike, avoiding the need for classic saving of registers as one program calls another. It is curious that 25 years after the initial design of the S/360 (which did not include a push-down stack), one was added to the architecture. Various instructions are provided to examine and modify the contents of the current linkage-stack entry.

In 2000, z/Architecture was introduced. Z added 64-bit addressing to the existing 24- and 31-bit addressing, resulting in the addition of the extended-addressing-mode control in the PSW.

All of this background material describes features of the architecture that are manipulated by the dual-address-space (DAS) facility:

- PSW: Access key (4 bits), problem/supervisor-state (1 bit), address-space control (2 bits), and addressing mode control (2 bits)

- · CR1: Primary address-space-control element (ASCE)

- CR3: Secondary address-space-second-table instance number (SASTEIN); PSW key mask; secondary address-space number (ASN)

- · CR4: Primary ASTEIN; authorization index; primary ASN

- · CR5: Primary address-space-second-table (ASTE) origin

- CR7: Secondary ASCE

- · CR8: Extended-authority index (& al)

- CR15: Linkage-stack-entry address.

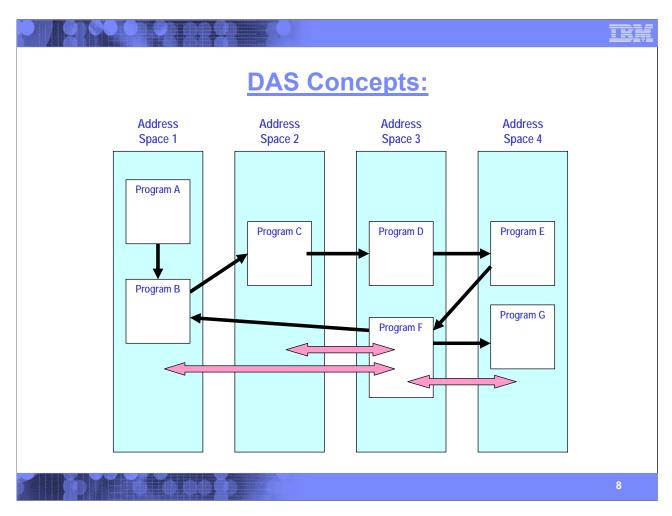

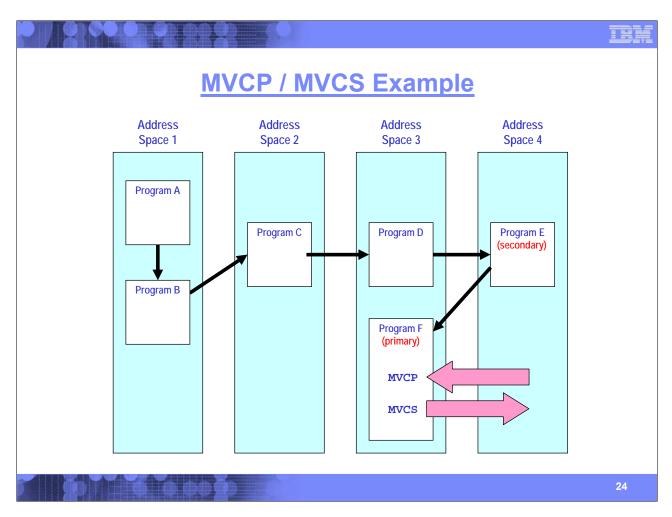

This slide illustrates some of the basic concepts in a dual-address-space environment.

[CLICK] Here we see four separate address spaces (AS).

[CLICK] Program A is executing in AS 1.

[CLICK] Program A calls program B, still in AS 1.

[CLICK] Program B calls program C, but now control has transferred to AS 2.

[CLICK] Program C calls program D in AS 3.

[CLICK] Program D calls program E in AS 4.

**[CLICK]** So as not to give the impression that this is a uni-directional process, we now see program E call program F (which is back in AS 3).

[CLICK] Now, program F calls program B, back in AS 1. This illustrates that a program may (albeit circuitously) call itself. Hopefully, program B is reentrant, reusable, and refreshable!

[CLICK] Program B returns to program F, which in turn ...

[CLICK] ... calls program G in AS 4.

[CLICK] Program G returns to program F.

[CLICK] Here we show that data movement can occur between program F in AS 3 and the data in AS 2.

[CLICK] ... or in AS 1

[CLICK] ... or in AS 4.

|                                                                                                             | TBM        |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

|                                                                                                             |            |  |  |  |  |  |

| DAS Feature Controls                                                                                        |            |  |  |  |  |  |

| CR 0: Miscellaneous controls                                                                                |            |  |  |  |  |  |

| CR 1: Primary address-space control element (PASCE) Region-table, segment-table, or real-space-token origin | SPSXR DTDL |  |  |  |  |  |

| CR 3: Secondary-space controls, PKM                                                                         |            |  |  |  |  |  |

| Secondary ASTE Instance # (SASTEIN) * PSW Key Mask (PKM) Second                                             | ndary ASN  |  |  |  |  |  |

| CR 4: Primary-space controls, AX                                                                            |            |  |  |  |  |  |

| Primary ASTE Instance # (PASTEIN) * Authorization Index (AX) Print                                          | hary ASN   |  |  |  |  |  |

| CR 5: Primary-ASN-Second-Table Origin                                                                       |            |  |  |  |  |  |

| Primary ASTE Origin (PASTE                                                                                  | ))         |  |  |  |  |  |

| CR 7: Secondary address-space control element (SASCE)                                                       |            |  |  |  |  |  |

| Region-table, segment-table, or real-space-token origin         GPSXR         DT                            |            |  |  |  |  |  |

| CR 13: Home address-space control element (HASCE)                                                           |            |  |  |  |  |  |

| Region-table, segment-table, or real-space-token origin         GPSXR         DT                            |            |  |  |  |  |  |

| CR 14: ASN-translation control & ASN 1 <sup>st</sup> -table origin                                          |            |  |  |  |  |  |

| C A                                                                                                         | ТО         |  |  |  |  |  |

|                                                                                                             |            |  |  |  |  |  |

|                                                                                                             | 9          |  |  |  |  |  |

This slide illustrates the various controls that affect the execution of the dual-address space (we'll show a few more controls that affect the linkage stack later in the presentation).

• CR0: Bit 36 (E) is the extraction-authority control, required to execute various EXTRACT instructions. Bit 37 (S) is the secondary-space control, required to access the secondary address space. Bit 44 (A) is the ASN-and-LX-reuse-facility (ALRF) control which enables the facility.

• CR1: The primary address-space control element (ASCE) provides controls affecting the primary address space, and a pointer to the real or absolute address of the root DAT table used in primary-space translations.

• CR3: Contains various information about the secondary address space, and the PSW key mask. The PKM is a 16-bit field, each bit of which represents one of the 16-possible storage-protection keys in the PSW. For certain DAS instructions, the PKM acts as an extension to the access-control bits in the PSW.

• CR4: Contains various information about the primary address space, and the authorization index used to authorize various instructions.

• CR5: Provides a 31-bit real pointer to the primary address-space second-table entry (ASTE). We'll see how this works shortly.

• CR7: The secondary ASCE provides controls affecting the secondary address space, and a pointer to the real or absolute address of the root DAT table used in secondary-space translations.

• CR13: The home ASCE provides controls affecting the primary home space, and a pointer to the real or absolute address of the root DAT table used in home-space translations.

• CR14: The leftmost 19 bits of a 31-bit real address pointing to the authorization table used in various instructions. Also, the C bit (bit 44) enables authorization processing.

Note, CRs 3 and 4 contain a secondary and primary ASTE instance number in the leftmost 32 bits. This field is meaningful only when the ASN-and-LX-reuse facility (ALRF) is installed, as indicated by an asterisk (\*) in subsequent slides. Although the ALRF is discussed in many of the slides, this presentation does not provide a comprehensive analysis of its operation.

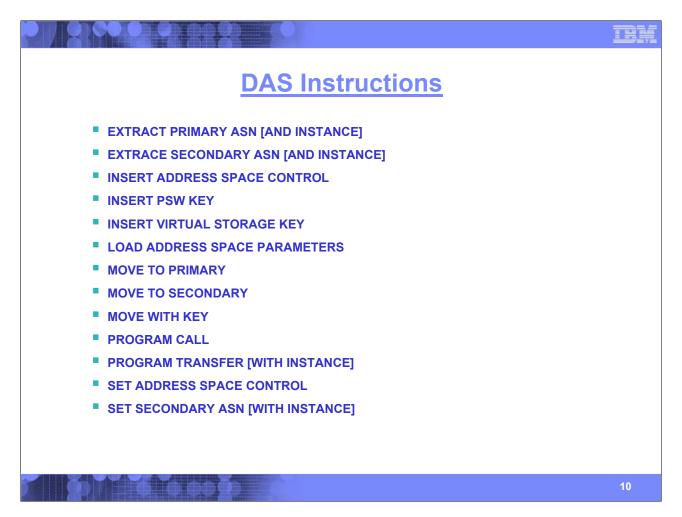

This slide lists the instructions that are part of the dual-address-space facility. Note, all of these instructions are either privileged or semiprivileged, as will be explained.

We'll investigate each of these (some in more detail than others) ... for lack of a better order, we'll look deal with them in alphabetic order.

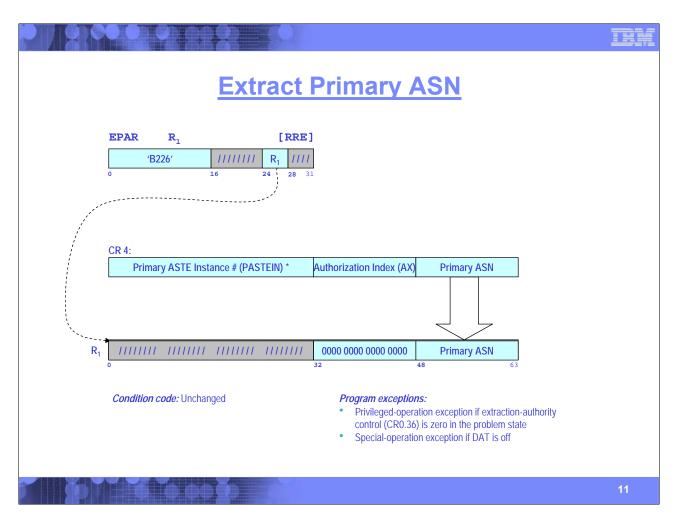

EXTRACT PRIMARY ASN (EPAR) provides the means by which the program can inspect the primary ASN in bits 48-63 of CR4. The architecture provides for up to 65,536 address spaces (many more address spaces can exist, but within the constraints of DAS, 64K is the limit).

[CLICK] EPAR is an RRE-format instruction with a single register designated by the R<sub>1</sub> field.

[CLICK] The rightmost 16 bits of control register 4 contain the primary ASN (PASN) to be copied to the first-operand register.

[CLICK] In addition to copying the PASN, the instruction sets bits 32-47 to zeros.

Remember that extraction-authority (E) bit we discussed a few slides back? If the E bit (bit 36 of CR0) is not one, a privileged-operation exception is recognized if the instruction is executed in the problem state. No such exception is recognized in the supervisor state. Also, since DAS is relevant only when DAT is on, the instruction recognizes a special-operation exception if DAT is off.

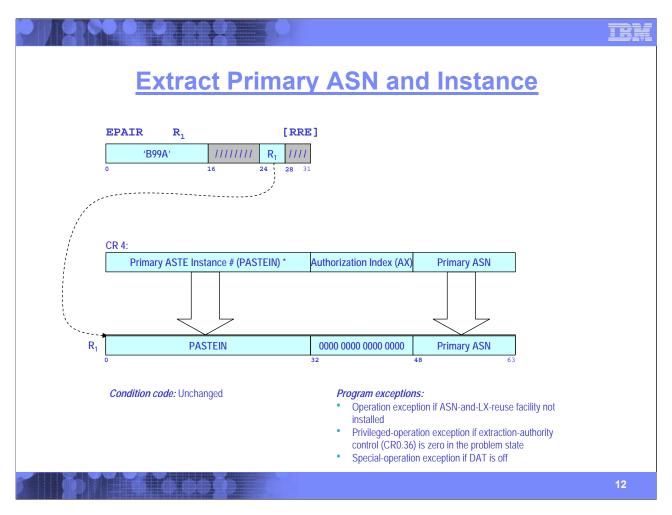

When the ASN-and-LX-reuse facility (ALRF) is installed, a variation of the EPAR instruction is available.

First a bit about ALRF: This facility allows certain resources used by DAT to be safely reused throughout the life of an OS by adding an instance number to the resource. The resources include the primary and secondary ASNs (in CRs 4 and 3, respectively), and the linkage indices used in the PROGRAM CALL instruction. ALRF was added with the z990 series of processors.

The primary ASN-second-table-entry instance number was added to previously unassigned leftmost word of CR4. The EXTRACT PRIMARY ASN AND INSTANCE (EPAIR) instruction does all of the operation of EPAR, but also includes the instance number in the leftmost word of the first-operand register.

[CLICK] ... as with previous slide.

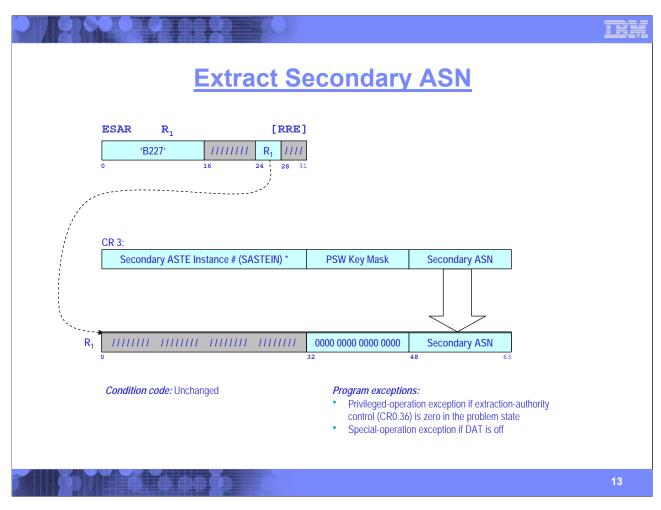

ESAR is similar to EPAR, except that the secondary ASN is extracted from control register 3. **[CLICK]** ... as with previous slide.

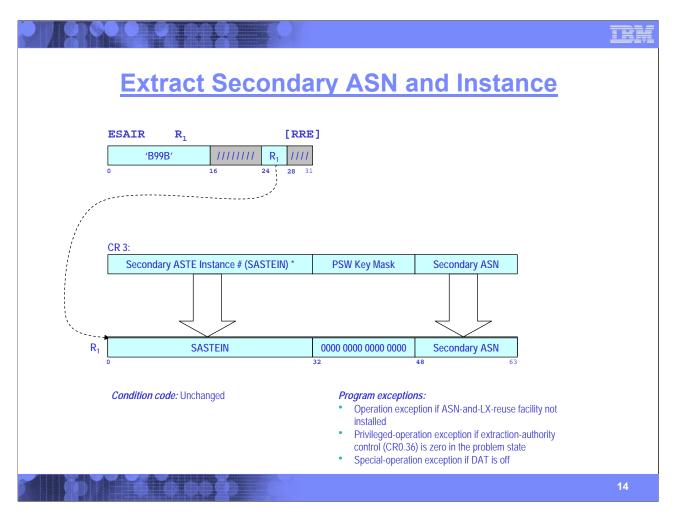

ESAIR is similar to EPAIR, except that the secondary ASTE instance number and ASN are extracted from control register 3. [CLICK] ... as with previous slide.

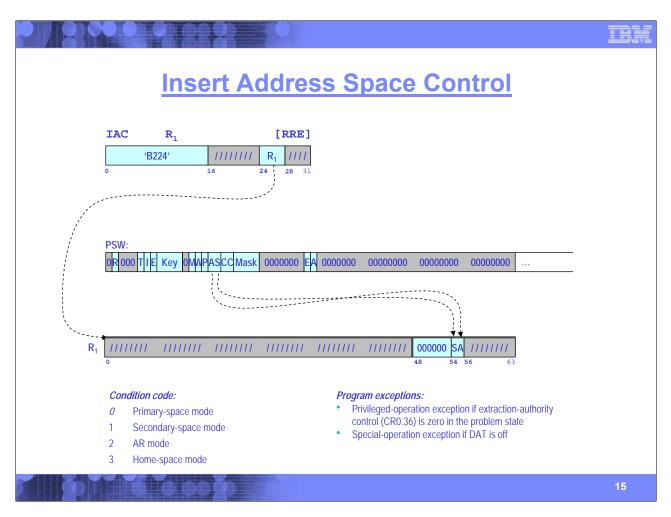

INSERT ADDRESS SPACE CONTROL provides a means by which the program can determine the current address-space control in the PSW.

[CLICK] IAC is an RRE-format instruction with a single register operand in designated by the R<sub>1</sub> field of the instruction.

**[CLICK]** The two address-space-control bits of the PSW (bits 16 and 17) are reversed, and placed in bit positions 54 and 55 of the first-operand register. These (reversed) bits are also used to set the condition code. The remainder of the byte (bits 48-53) in the register are set to zeros, and all other bits in the register are unchanged.

So why are the bits reversed? When DAS was originally introduced, there was a single primary/secondary bit in bit 16 of the PSW. When the advanced-space facility was introduced (adding AR- and home-space modes), PSW bit 17 was added, thus the encodings were 00=primary, 01=AR, 10=secondary, 11=home. IAC originally inserted just 1 bit (PSW bit 16, the primary/secondary indication) in bit 23 of a 32-bit register (bit 55 of a 64-bit register). To facilitate handling by the program, it was desirable to have both bits in the same byte, thus PSW bit 17 was placed in bit 22 of a 32-bit register (bit 54 of a 64-bit register).

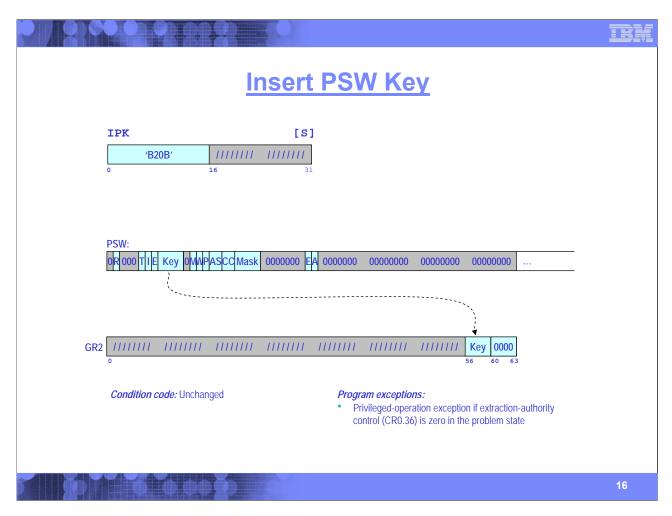

INSERT PSW KEY is used to inspect the current access-control bits in the PSW.

**[CLICK]** Note, IPK is somewhat unusual as it does not have a register specification built into the instruction itself. IPK is called an S-format instruction, suggesting that it might have had a storage operand, but it could also be thought of as an RRE-format instruction with no register operands. The operand of the instruction is always general register 2.

[CLICK] The instruction takes bits 8-11 of the current PSW and places them in bits 56-59 of general register 2, with bits 60-63 of the register set to zero.

Also note that because the IAC instruction (described on the previous slide) places its results in bits 54 and 55 of a register, IAC can share the same result register with IPK.

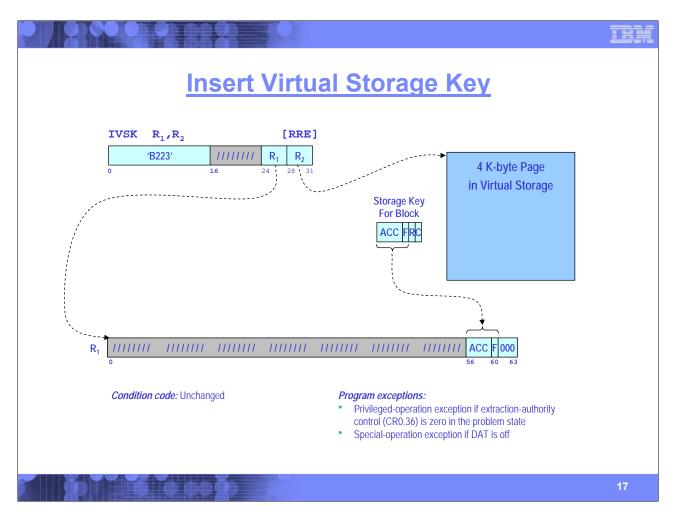

INSERT VIRTUAL STORAGE KEY performs dynamic address translation on the location specified by the second-operand register, and places the access-control and fetch-protection bits from the storage key for that block into the first-operand register.

[CLICK] The second-operand registerdesignates a 4 K-byte page in virtual storage.

[CLICK] The first-operand register will receive the result.

[CLICK] Corresponding the the 4 K-byte block of real storage associated with the second-operand virtual address, there is a 7-bit storage-protection key.

[CLICK] The 4-bit access-control bits from the key, and the 1-bit fetch-protection bit from the key are placed in bits 56-59 and bit 60, respectively, of the first-operand register. Bits 61-63 of the register are set to zeros.

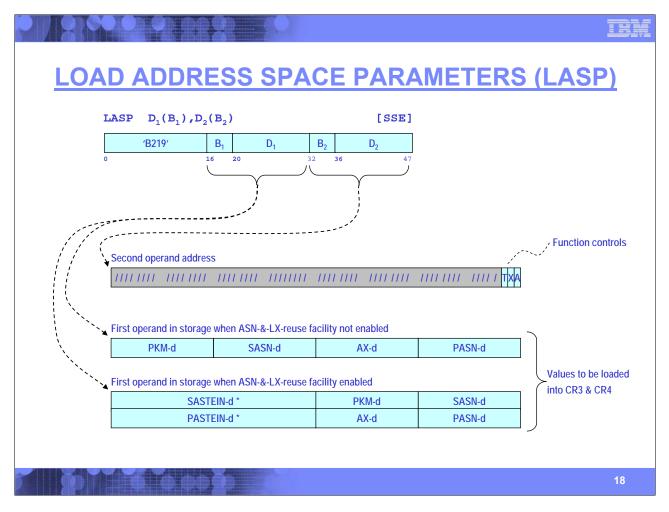

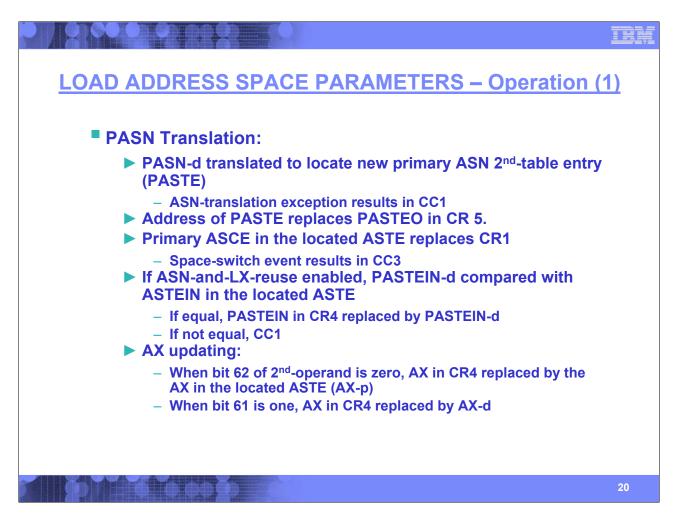

LOAD ADDRESS SPACE PARAMETERS provides a means by which an operating system dispatcher can establish a DAS environment.

The key control registers that designate the environment are CRs 3 and 4, containing the secondary and primary space identifications, the PSW key mask, and the authorization index. When the ASN-and-LX-reuse facility is enabled, CRs 3 and 4 also contain instance numbers for the secondary and primary ASNs.

[CLICK] The first operand of LASP is a location in storage that contains the context to be loaded into CRs 3 and 4. When the ASN-and-LX-reuse facility is not enabled, the first operand is a doubleword, the first word of which is loaded into the rightmost half of CR3, and the second word of which is loaded into the rightmost half of CR4.

[CLICK] When the ASN-and-LX-reuse facility is enabled, the first operand is a location in storage that contains two doublewords. These doublewords exactly represent the information loaded into CRs 3 and 4.

Up until now, this instruction looks remarkably similar to a LOAD CONTROL instruction that loads CRs 3 and 4. However, LASP is much more powerful than a simple LCTL or LCTLG. Additional processing may be performed, as described on the following slides.

[CLICK] The second-operand is not used to access storage. Rather, the rightmost 3 bits of the second-operand address contain function controls that determine how additional processing is to be performed.

| 1 (T) ASN translation performed only when old and new ASN are different.                     | ASN translation performed      |

|----------------------------------------------------------------------------------------------|--------------------------------|

|                                                                                              | Activitation performed         |

| 2 (X) AX associated with new PASN used.                                                      | AX in first operand used       |

| 3 (A) SASN authorization performed                                                           | SASN authorization not perform |

| PASN-d. When SASN-d = PASN-d, SSCE<br>equal to PASTEIN (if ASN&LX-reuse is ena<br>performed. |                                |

This slide enumerates the function controls in the rightmost three bits of the second-operand address.

ASN translation is a function that is described as a part of the PROGRAM TRANSFER instruction. Given a 16-bit address-space number, ASN translation locates an address-space-second-table entry (ASTE) containing additional context and authorization information for an address space.

Bit 61 controls whether ASN translation is always performed by LASP, or only when the designated ASN (SASN-d or PASN-d) in the first operands differ from the current SASN or PASN.

Bit 62 controls whether the authorization index (AX, used in the ASN-translation process) is associated with the new PASN (as a result of ASN translation, or if it is associated with the designated AX (AX-d) in the first operand.

Bit 64 controls whether secondary ASN translation is performed.

When primary ASN translation is performed, LASP locates a new primary address-space second-table entry (ASTE) by means of ASN translation. If ASN translation fails, rather than presenting an exception (as is done in PROGRAM TRANSFER), LASP simply sets condition code 1.

If the translation is successful:

- (1) If ASN-and-LX-reuse is enabled, the designated primary ASTE instance number (PASTEIN-d) in the first operand is compared with the ASTEIN in the newly-located ASTE. If equal, the PASTEIN in CR4 is replaced by the PASTEIN-d; if not, the instruction completes with condition code 1.

- (2) The address of the newly-located primary ASTE is loaded into CR5.

- (3) The address-space control element (ASCE) from the new primary ASTE is loaded into CR1, becoming the new primary ASCE.

- (4) If bit 62 of the second-operand address is zero, the authorization index in CR4 is replaced by the AX in the newly-located ASTE. Otherwise (when bit 62 is one), the AX in CR4 is replaced by the AX designated in the first operand (AX-d).

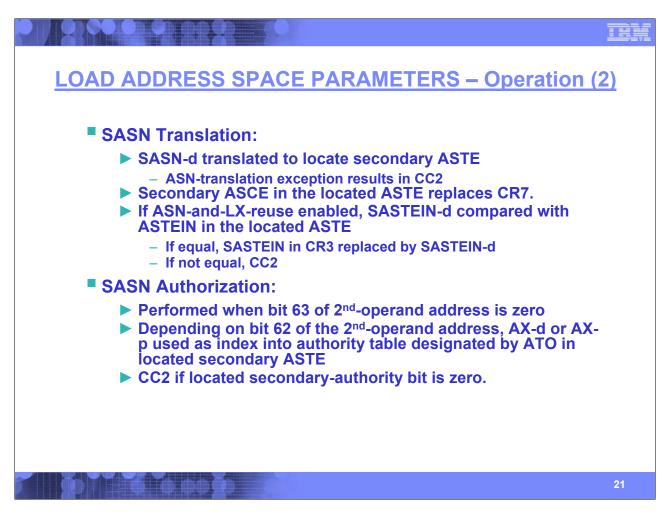

When secondary ASN translation is performed, LASP locates a new address-space second-table entry (ASTE) by means of ASN translation. If ASN translation fails, rather than presenting an exception (as is done in PROGRAM TRANSFER), LASP simply sets condition code 2.

If the translation is successful:

- (1) If ASN-and-LX-reuse is enabled, the designated seconary ASTE instance number (PASTEIN-d) in the first operand is compared with the ASTEIN in the newly-located ASTE. If equal, the SASTEIN in CR3 is replaced by the SASTEIN-d; if not, the instruction completes with condition code 2.

- (2) The address-space control element (ASCE) from the new secondary ASTE is loaded into CR7, becoming the new secondary ASCE.

- If bit 63 of the second-operand address is zero, the secondary authorization is to be performed. Depending on bit 62 of the secondoperand address, either the designated authorization index from the first operand (AX-d) or the AX from the primary ASTE is used as an index into an authority table in the newly-located secondary ASTE. If the designated secondary-authority bit is zero, then the instruction completes with CC2 (and no control registers are modified).

- This description of LASP does not go into the level of detail that is provided for some of the other DAS instructions (such as PROGRAM CALL). For additional details, see the instruction description in the *z*/Architecture Principles of Operation (SA22-7832).

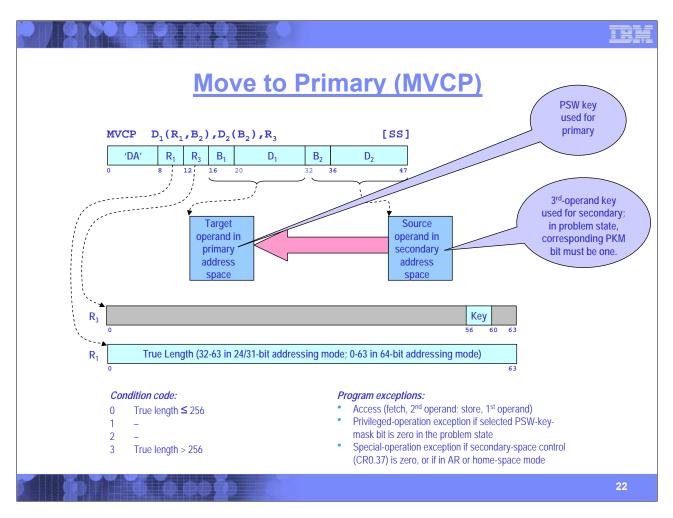

MOVE TO PRIMARY provides a means by which a semi-privileged program can move data to the primary address space from the secondary address space.

[CLICK] The second operand is the source operand ... a storage location in the secondary address space.

[CLICK] The first operand is the target operand ... a storage location in the primary address space.

**[CLICK]** The  $R_1$  field of the instruction designates a register containing the true length of the operand. The instruction is capable of moving up to 256 bytes in a single execution. If the true length is greater than 256, a condition code indicates that not all of the first operand was moved.

[CLICK] The R<sub>3</sub> field of the instruction designates a register containing a four-bit storage-protection key, used in addition to the PSW key.

[CLICK] The data are moved from the second-operand location (secondary space) to the first-operand location (primary space).

[CLICK] The PSW key is used for the first operand's location.

[CLICK] The key designated in the third operand register is used for access to the second operand's location.

Thus far, we haven't discussed the PSW key mask in control register three. This instruction is one place where the PKM is used. In the problem state, the 4-bit key in the third operand contains a value of 0-15. This value is used as an index into the 16-bit PKM in CR3 to locate a bit which must be one in the problem state; otherwise, a privileged-operation exception is recognized. In the supervisor state, the PKM is not examined, and the key in the third operand is considered to always be authorized.

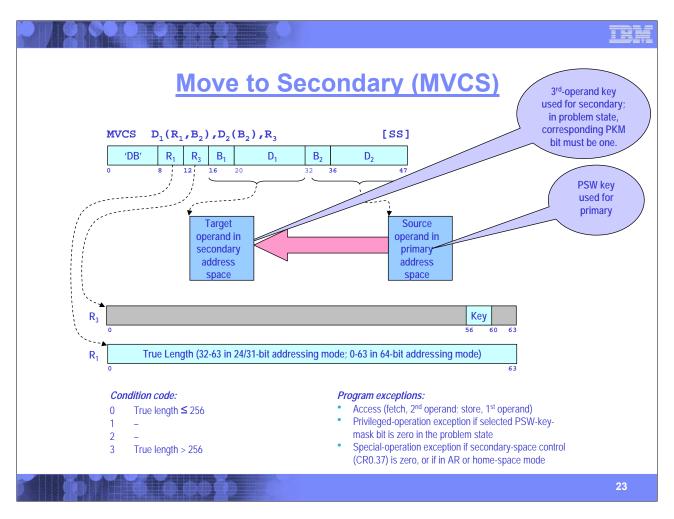

MOVE TO SECONDARY works similar to MOVE TO PRIMARY, except that the address spaces are reversed.

[CLICK] The second operand is the source operand ... a storage location in the secondary address space.

[CLICK] The first operand is the target operand ... a storage location in the primary address space.

**[CLICK]** The  $R_1$  field of the instruction designates a register containing the true length of the operand. The instruction is capable of moving up to 256 bytes in a single execution. If the true length is greater than 256, a condition code indicates that not all of the first operand was moved.

[CLICK] The R<sub>3</sub> field of the instruction designates a register containing a four-bit storage-protection key, used in addition to the PSW key.

[CLICK] The data are moved from the second-operand location (primary space) to the first-operand location (secondary space).

[CLICK] The PSW key is used for the second operand's location.

[CLICK] The key designated in the third operand register is used for access to the first operand's location.

Note that for both MVCP and MVCS, the PSW key is used to control access to the operand in the primary space; the key designated in the third operand is used to access the operand in the secondary space.

This slide provides an example of MVCP and MVCS, using the address-space example shown earlier. Although we haven't yet discussed PROGRAM CALL (PC), whenever a program calls another program in a different address space using PC, the newly-called space becomes the primary space, and the calling space becomes the secondary.

[CLICK] So, here we see that the most-recently called program F is executing in the primary address space (space 3), and program E is executing in the secondary address space (space 4).

[CLICK] Executing a MVCP instruction in this context causes data to be moved from space 4 (the secondary) to space 3 (the primary).

[CLICK] Executing a MVCS instruction in this context causes data to be moved from space 3 (the primary) to space 4 (the seconary).

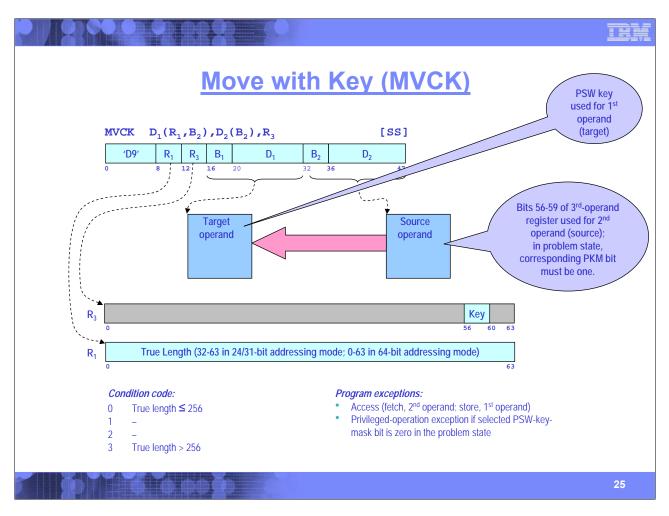

MOVE WITH KEY is similar to MVSC and MVCP, except without data are moved within the same address space, but using different storage-protection keys for the first- and second-operand locations.

[CLICK] The second operand is the source operand.

[CLICK] The first operand is the target operand.

**[CLICK]** The  $R_1$  field of the instruction designates a register containing the true length of the operand. The instruction is capable of moving up to 256 bytes in a single execution. If the true length is greater than 256, a condition code indicates that not all of the first operand was moved.

[CLICK] The R<sub>3</sub> field of the instruction designates a register containing a four-bit storage-protection key, used in addition to the PSW key.

[CLICK] The data are moved from the second-operand location to the first-operand location.

[CLICK] The PSW key is used for the first operand's location.

**[CLICK]** The key designated in the third operand register is used for access to the second operand's location. In the problem state, the bit in the PKM corresponding to the key in the third-operand register must be one; otherwise, a privileged-operation exception is recognized.

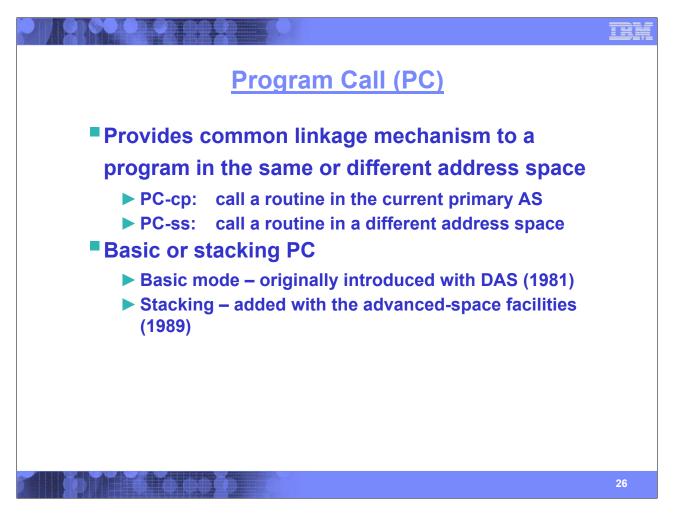

PROGRAM CALL (PC) is an extremely powerful instruction that distinguishes z/Architecture from other more RISC-like architectures. We're going to dedicate several slides to its various functions.

When PROGRAM CALL is used to call a routine in the current primary address space, it is called a current-primary PROGRAM CALL (PC-cp). When PROGRAM CALL is used to call a routine a different address space, it is called a space-switching PROGRAM CALL (PC-ss).

The original PC architecture was introduced with the dual-address-space facility in 1981. Additional functions were added to the PC architecture with the advent of the advanced-space facilities (ASF) in 1989; with these advances, the instruction can now be either a basic PC (which operates like the original PC, and does not use the linkage stack), or a stacking PC (which uses the linkage stack).

Regardless of whether the instruction is basic or stacking, it can also be PC-cp or PC-ss, thus four combinations are possible.

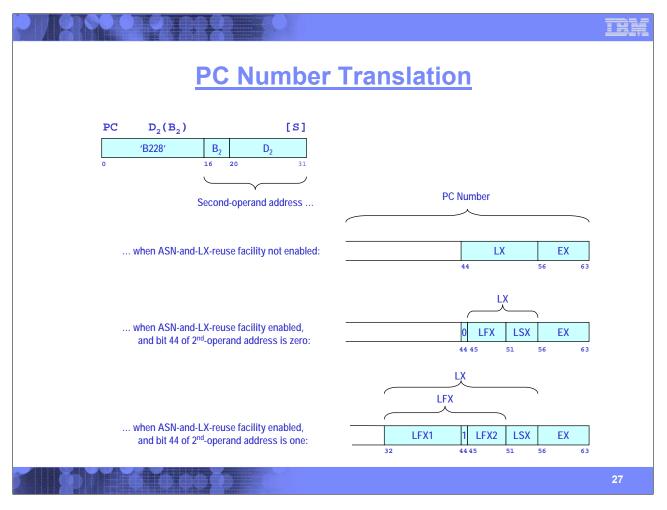

Regardless of which form of PC is used, the instruction format is the same. The operand of the PC instruction is not used to access storage; rather, the rightmost bits of the operand address form what is called a PC number.

In the original PC, the PC number is a 24-bit value that is split into a 12-bit linkage index (LX) and an 8-bit entry index (EX). The ASNand-LX-reuse facility (added with the z990) provides the option of having an extended 31-bit PC number which, curiously, has a bit in the middle indicating which of two formats are used. In the extended PC number, the linkage index (LX) is broken into a first and second part (LFX and LSX, respectively), and when bit 44 of the operand address is one, the LFX is a set of discontiguous bits with bit 44 in the middle!

If you've ever examined other parts of the architecture closely, you'll notice that there are a lot of values that are chopped into smaller indices. A prime example is a virtual address which may be divided into up to three region indices, a segment index, page index, and byte index. The reason for the division is that each of these indices is used by the machine to find an entry in a table that resides in real or absolute storage. As it is *extremely* difficult for most operating systems to consolidate large blocks of real or absolute storage into a contiguous block that can be indexed by a large value, these tables are kept relatively small, and a higher-level index is used to locate an entry that designates a subordinate table used by a lower-level index.

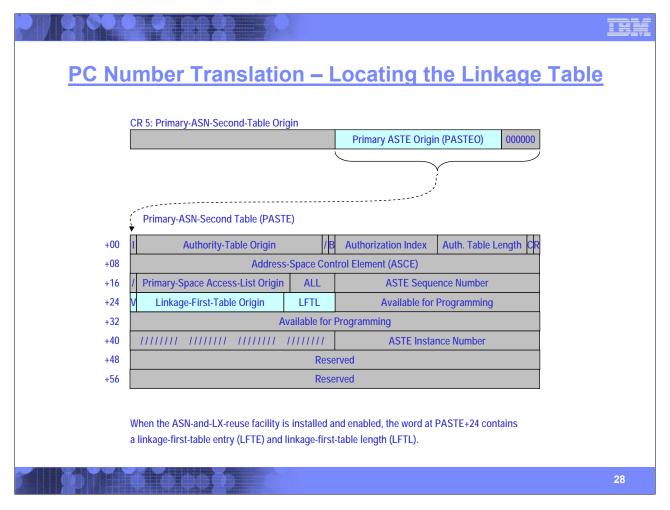

This slide illustrates the beginning of PC number translation ... that is, the process of taking a PC number and locating something useful from it.

[CLICK] The rightmost bits of control register 5 contain the primary address-space-table-entry origin (PASTEO). The PASTEO, with 6 binary zeros appended on the right, form the address of the primary ASTE (PASTE).

[CLICK] When the ASN-and-LX-reuse facility is not enabled, the word at PASTE+24 contains a validity bit, a linkage-table origin, and a linkage-table length.

[CLICK] When the ASN-and-LX-reuse facility is enabled, the word at PASTE+24 contains a validity bit, a linkage-<u>first</u>-table origin, and a linkage-<u>first</u>-table length.

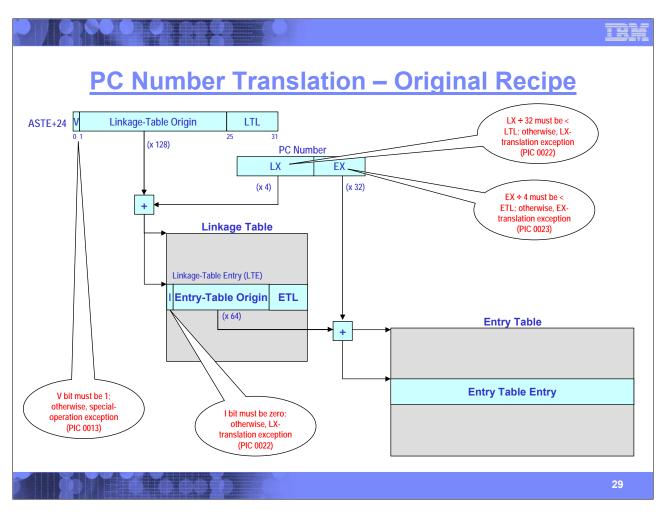

This slide shows the process of PC-number translation when the ASN-and-LX-reuse facility is not installed.

[CLICK] First, the validity bit (bit 0 of the word at the PASTE+24) must be one for PC-number translation to occur. Otherwise, a special-operation exception is recognized; the special-operation exception has a program-interruption code (PIC) of 0013 hex.

[CLICK] The linkage-table origin in the PASTE, with 7 zeros appended on the right, forms a 31-bit real address of the linkage table.

[CLICK] The linkage index in the PC number is checked to ensure that it does not exceed the linkage-table length (in the word at PASTE+24). If the LX exceeds the linkage-table length, a LX-translation exception is recognized (PIC 0022 hex).

[CLICK] The LX in the PC number is used to locate an entry in the linkage table (LTE).

[CLICK] The invalid bit (bit 0 of the LTE) must be zero; otherwise, a LX-translation exception is recognized (PIC 0022 hex).

[CLICK] The entry-table origin in the LTE, with six binary zeros appended on the right, forms a 31-bit real address of the entry table.

[CLICK] The entry index in the PC number is checked to ensure that it does not exceed the entry-table length (in the rightmost bits of the LTE). If the EX exceeds the entry-table length, an EX-translation exception is recognized (PIC 0023 hex).

[CLICK] The entry index is used to locate an entry-table entry.

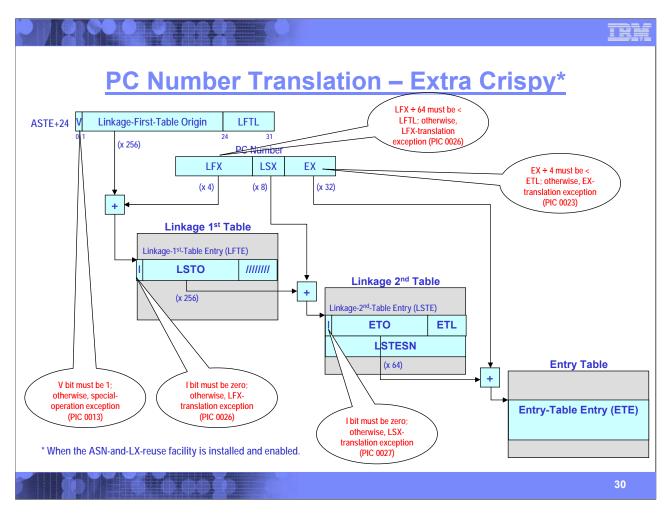

This slide illustrates the process of PC-number translation when the ASN-and-LX-reuse facility is enabled. The process is similar to that when ALRF is not installed, but with the differences noted below:

**[CLICK]** As with non-ALRF PC, we fist check the validity bit (bit 0 of the word at the PASTE+24) which must be one for PC-number translation to occur. Otherwise, a special-operation exception is recognized; the special-operation exception has a program-interruption code (PIC) of 0013 hex.

[CLICK] The linkage-first index (LFX) in the PC number is checked to ensure that it does not exceed the linkage-table length (in the word at PASTE+24). If the LFX exceeds the linkage-table length, a LX-first-translation exception is recognized (PIC 0026 hex).

[CLICK] The LFX in the PC number is added to the linkage-first-table origin to locate an entry in the linkage-first table (LFTE).

[CLICK] The invalid bit (bit 0 of the LFTE) must be zero; otherwise, a LFX-translation exception is recognized (PIC 0026 hex).

[CLICK] The linkage-second index (LSX) in the PC number is added to the linkage-second-table origin (LSTO, found in the LFTE) to locate an entry in the linkage-second table (LSTE). Note that unlike the LFX, which is checked for a maximum length, there is no checking of a maximum LSX value.

[CLICK] The invalid bit (bit 0 of the LSTE) must be zero; otherwise, a LSX-translation exception is recognized (PIC 0027 hex).

[CLICK] The entry index in the PC number is checked to ensure that it does not exceed the entry-table length (in the rightmost bits of the LSTE). If the EX exceeds the entry-table length, an EX-translation exception is recognized (PIC 0023 hex).

[CLICK] The entry-table origin in the LSTE, with six binary zeros appended on the right, forms a 31-bit real address of the entry table. The entry index (EX) in the PC number, multiplied by 32, is used to locate the entry-table entry (ETE) in the entry table.

Regardless of whether ALRF is enabled, the results of the original-recipe or extra-crispy PC-number translation is an entry-table entry, described in the following slide.

|                       |                                                                                      |       |                                                                                                                                                                             | ibm |  |  |

|-----------------------|--------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| PC: Entry-Table Entry |                                                                                      |       |                                                                                                                                                                             |     |  |  |

| +00                   | Entry Instruction Address (EIA)                                                      |       |                                                                                                                                                                             |     |  |  |

| +08                   | Auth. Key Mask (AKM) Address Space Number                                            | Entry | Key Mask (EKM) ////////////////////////////////////                                                                                                                         |     |  |  |

| +16                   | TG/KMECS EK //// Entry Ext. Auth. Index                                              | / Ac  | ddress Space 2 <sup>nd</sup> -Table Origin //////                                                                                                                           |     |  |  |

| +24                   | Entry Parameter                                                                      |       | r                                                                                                                                                                           |     |  |  |

|                       |                                                                                      |       |                                                                                                                                                                             |     |  |  |

| Р                     | 0: Supervisor state<br>1: Problem state                                              | E     | 0: EAX (CR8.32-47) unchanged<br>1: EAX replaced by entry EAX (EEAX)                                                                                                         |     |  |  |

| т                     | 0: Basic program call<br>1: Stacking program call                                    | С     | 0: PSW ASC set to primary-space mode (00)<br>1: PSW ASC set to home-space mode (01)                                                                                         |     |  |  |

| G                     | 0: EIA is 24- or 31-bit address (based on bit 32)                                    | EK    | Entry key                                                                                                                                                                   |     |  |  |

| Follo                 | 1: EIA is 64-bit address<br>wing fields meaningful only when T=1:                    | S     | 0: New SASN (CR3.48-63) set from old PASN (in CR4.48-63)<br>New SASCE (CR7) set from old PASCE (CR1)                                                                        |     |  |  |

| K                     | 0: PSW key remains unchanged<br>1: PSW key replaced by entry key (EK)                |       | New SASEE (CK7) set from old PASEE (CK7)<br>New SASTEIN (CR3.0-31) set from old PASTEIN (CR4.0-31)<br>1: New SASN set equal to new PASN<br>New SASCE set equal to new PASCE |     |  |  |

| Μ                     | 0: EKM is ORed into the PSW key mask (CR3.32-47)<br>1: EKM replaces the PSW key mask |       | New SASTEIN set equal to new PASTEIN                                                                                                                                        |     |  |  |

|                       | C111100                                                                              |       |                                                                                                                                                                             | 31  |  |  |

The entry-table entry contains a much of the information needed to call a program in a different address space. We'll explore most of these in exquisite detail in the following slides. However a few heads-up notices are warranted.

## [CLICK]

The P bit (bit 63 of the first doubleword) designates whether the called program will receive control in the supervisor or problem state (0 or 1, respectively).

The T bit (bit 0 of the third doubleword) designates whether the operation is a basic PC or a stacking PC (0 or 1, respectively). Except for the G bit (described below), the remaining G, K, M, E, C, S, and EK fields in the third doubleword are used only in stacking PC.

The G bit determines whether the called program receives control in the basic addressing mode (that is 24- or 31-bit mode) versus the 64-bit addressing mode (0 or 1, respectively). When G=0, the basic addressing mode is determined by bit 32 of the EIA field.

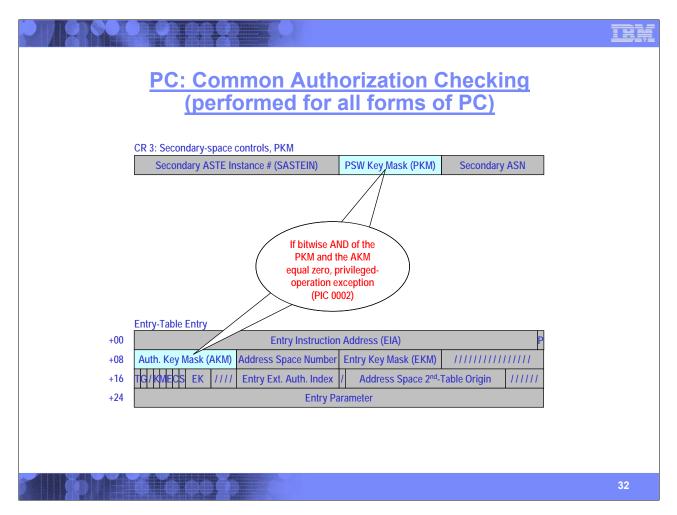

After locating the ETE designated by the PC number, an authorization test is performed. The ETE contains a 16-bit authorization-key mask (AKM) which is compared with the current PSW-key mask in control register 3.

If the logical AND of the AKM and the PKM is zero, then there is no intersection of the current key mask and what's available for the PC routine; in this case, a privileged-operation exception (PIC 0002 hex) is recognized.

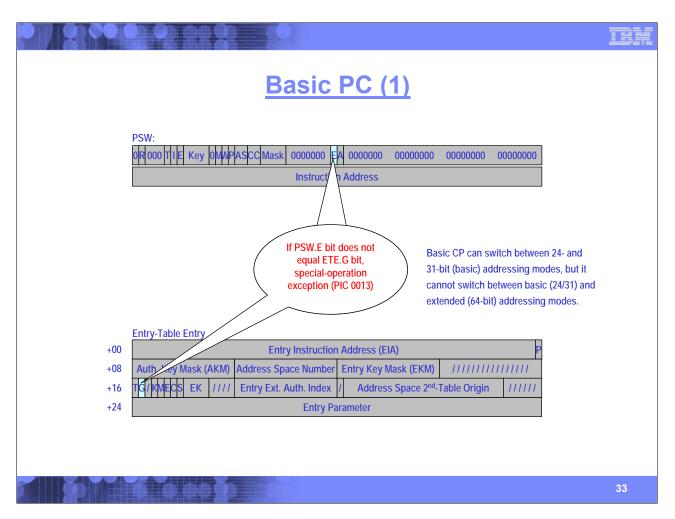

Whether or not a PROGRAM CALL instruction is a basic PC or a stacking PC is determined by the T bit (bit 0 of the 3<sup>rd</sup> doubleword of the ETE). The following series of slides addresses the operation of the basic PROGRAM CALL instruction.

In basic PC operation, the program is allowed to switch between 24- and 31-bit addressing (basic addressing mode), however the program is not allowed to switch between basic addressing and extended (i.e., 64-bit) addressing. If the extended-addressing (E) bit, bit 32 of the PSW does not match the corresponding G bit of the ETE, then a special-operation exception is recognized (PIC 0013 hex).

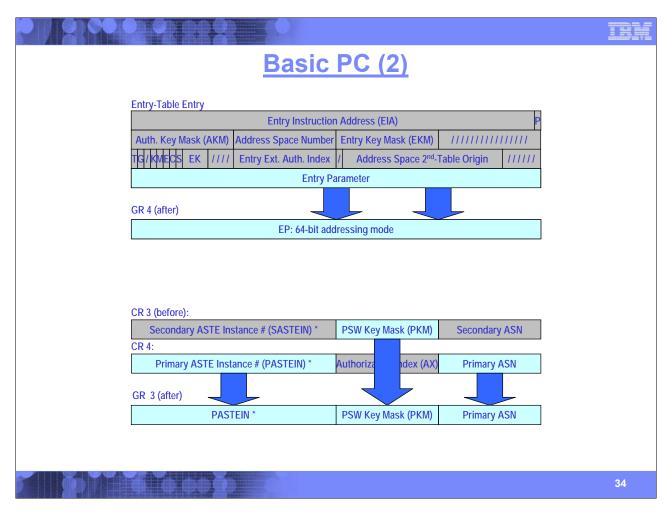

The basic PROGRAM CALL operation saves current context information in general registers 3, 4, and 14. An entry parameter contained in the ETE is made available to the program in general register 4.

**[CLICK]** If the called program is in the 24- or 31-bit addressing mode (that is, the G bit in the ETE is zero), then the rightmost 32 bits of the entry parameter and placed in bits 32-63 of general register 4; the remainder of GR4 is unchanged.

[CLICK] If the called program is in the 64-bit addressing mode, the entire entry parameter is placed into bits 0-63 of GR4.

Another result of PROGRAM CALL is that information about the current primary ASN and PSW key mask are placed into general register 3.

[CLICK] The contents of the current PSW key mask (in bits 32-47 of control register 3) and the primary ASN (in bits 48-63 of control register 4) are placed into bits 32-63 of general register 3.

**[CLICK]** If the ASN-and-LX-reuse facility is enabled, the contents of the primary ASTE instance number (PASTEIN, in bits 0-31 of control register 4) are placed into bits 0-31 of general register 3. If ALRF is not enabled, bits 0-32 of GR3 remain unchanged.

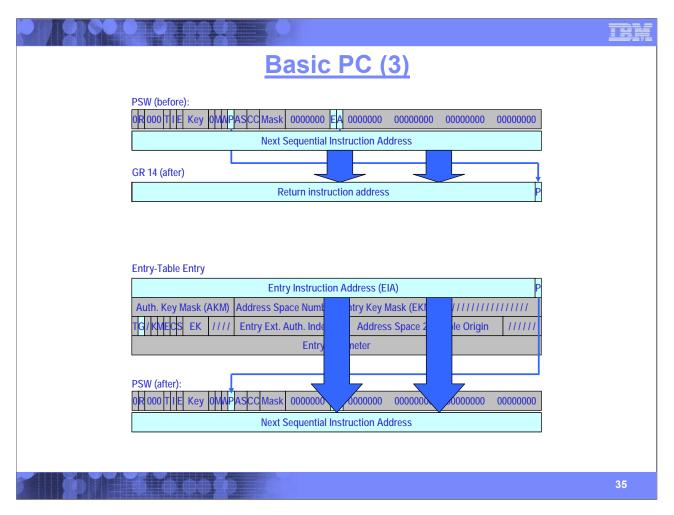

The PSW instruction address contains the address of the instruction following the PROGRAM CALL. The instruction address, basicaddressing-mode bit (when in the 24- or 31-bit addressing mode), and the problem-state bit of the PSW are preserved for use by the PROGRAM TRANSFER instruction, to allow returning to the caller.

[CLICK] These data are placed into general register 14.

**[CLICK]** In the 24- or 31-bit addressing mode, bits 33-62 of the PSW instruction-address field (bits 97-126 of the PSW) are placed in bits 33-62 of general register 14. The basic-addressing mode (bit 32 of the PSW) is placed in the corresponding bit of GR14, and the problem-state bit (bit 15 of the PSW) is placed in bit 63 of GR14.

[CLICK] In the 64-bit addressing mode, the bits 0-62 of the PSW are placed in the corresponding bits of general register 14, and the PSW problem-state bit is placed in bit 63 of GR14.

[CLICK] Next, the entry-instruction address (EIA) in the ETE is placed in the PSW that will receive control when the instruction completes.

**[CLICK]** In the 24- or 31-bit addressing mode, bits 33-62 of the EIA, with a zero on the right, are placed into bits 97-127 of the PSW instruction address (actually, PSW bits 97-126). Bit 32 of the EIA is placed in bit 32 of the PSW (the basic-addressing mode bit that selects between 24- and 31-bit addressing). Finally, bit 63 of the EIA becomes the new PSW problem-state bit (PSW bit 15).

[CLICK] In the 64-bit mode, bits 0-62 of the EIA, with a zero on the right, are placed into the PSW instruction address (PSW bits 64-127). Bit 63 of the EIA becomes the new PSW problem-state bit (PSW bit 15).

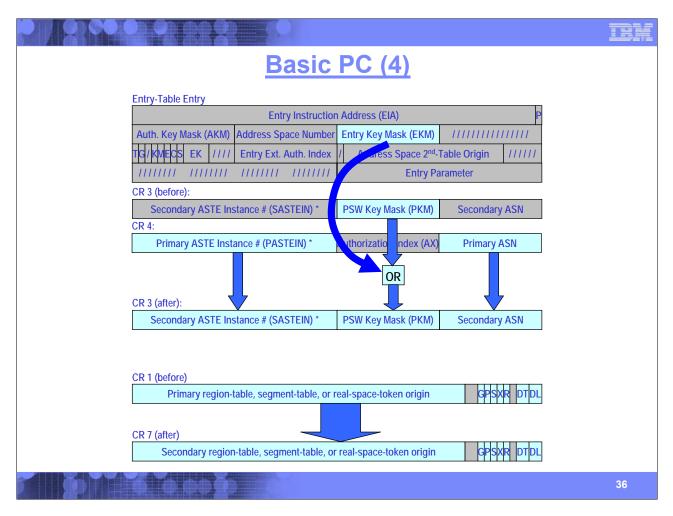

Next, we copy the current primary-space context to the secondary space:

[CLICK] The primary ASN in bits 48-63 of control register 4 is copied to the secondary ASN (in the corresponding bits of control register 3).

**[CLICK]** The entry-key mask in the ETE is logically ORed with the current PSW key mask in bits 32-47 of control register 3; the result replaces the PKM in CR3. The effect of this operation is to either the same PKM value or a PKM value with additional keys allowed. Thus, PC can increase the key authorization of the caller.

[CLICK] When the ASN-and-LX-reuse facility is enabled, the primary ASTE instance number (PASTEIN) in bits 0-31 of control register 4 is copied to the secondary ASTE instance number (SASTEIN) in the corresponding bits of CR3.

[CLICK] The last step in copying the space context is to copy the primary address-space control element (P-ASCE, in control register 1) into the secondary ASCE (in control register 7).

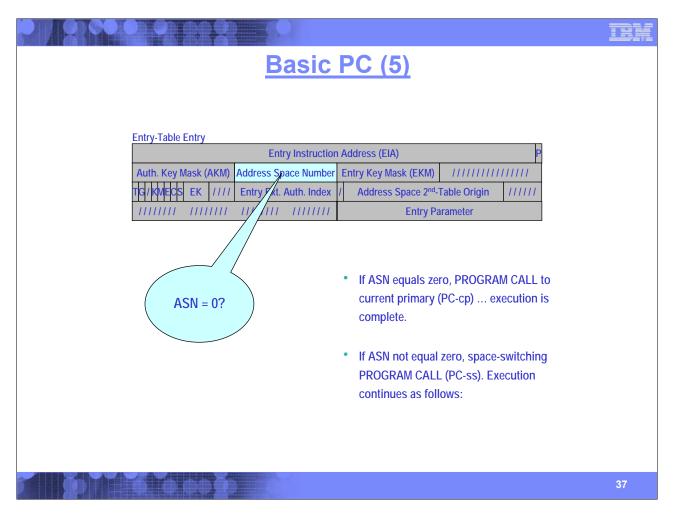

Bytes 11-12 of the entry table entry (located by PC-number translation) contains an address-space number (ASN).

[CLICK] If the ASN field in the ETE contains zero, then this is a PROGRAM CALL to the current primary address space (PC-cp), and execution of the instruction is complete. If the ASN field is not zero, the this is a space-switching PROGRAM CALL (PC-ss), and the description continues on the following slides.

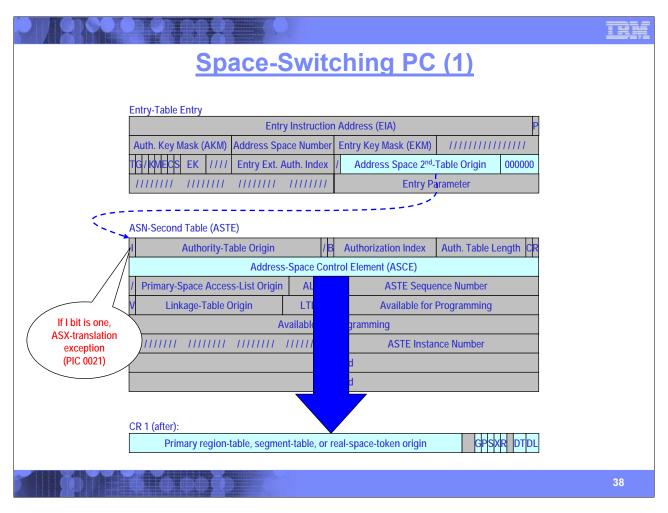

For a space-switching PROGRAM CALL (PC-ss), the word at ETE+20 contains a pointer to yet another table-entry in storage to be examined.

[CLICK] Bits 1-25 of the word at ETE+20, appended by six binary zeros on the right, form the 31-bit real address of the address-spacesecond-table entry (ASTE) representing the address space to which control is to be passed. If bit 0 of the ASTE is one, then the ASTE is invalid; in this case, instruction execution is suppressed, and an ASX-translation exception is recognized (PIC 0021 hex).

[CLICK] Assuming that the ASTE is valid, then bytes 8-15 of the ASTE represent the new primary address-space control element (P-ASCE). This value is loaded into control register 1.

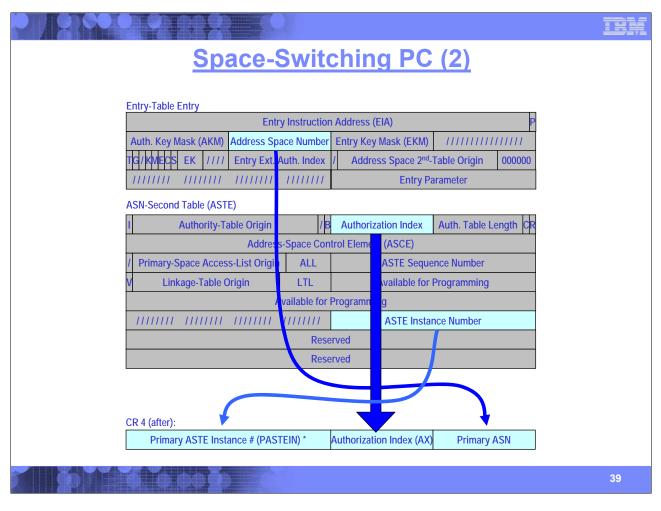

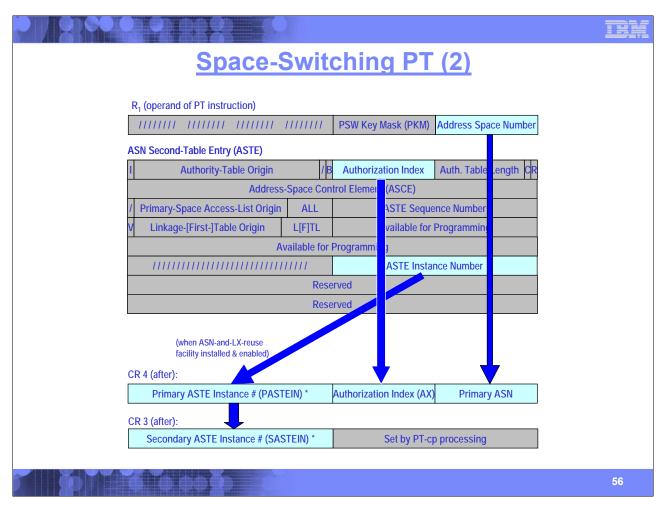

The next step in a space-switching PC is to update the primary context information in control register 4.

[CLICK] The address-space number in the entry-table entry (located by PC-number translation) is copied into the primary-ASN field in bits 48-63 of control register 4. Then, the authorization index in bits 32-47 of the newly-located address-space-second-table entry is copied into bits 32-47 of control register 4.

[CLICK] If the ASN-and-LX-reuse facility is enabled, the ASTE instance number in the newly-located ASTE is copied into bits 0-31 of control register 4; otherwise, bits 0-31 of CR4 remain unchanged.

|                                                                                                                                  | IBM |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Space-Switching PC (3)                                                                                                           |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

| Entry-Table Entry Entry Instruction Address (EIA) P                                                                              |     |  |  |  |  |  |  |

| Auth. Key Mask (AKM)         Address Space Number         Entry Key Mask (EKM)         ////////////////////////////////////      |     |  |  |  |  |  |  |

| TG/KMECS       EK       ////       Entry Ext. Auth. Index       /       Address Space 2 <sup>nd</sup> -Table Origin       000000 |     |  |  |  |  |  |  |

| /////// Entry neter                                                                                                              |     |  |  |  |  |  |  |

| CR 5 (after)                                                                                                                     |     |  |  |  |  |  |  |

| Primary ASTE Origin (PASTEO) 000000                                                                                              |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

|                                                                                                                                  | 40  |  |  |  |  |  |  |

|                                                                                                                                  |     |  |  |  |  |  |  |

One last step in a stacking PC:

**[CLICK]** The address-space second-table origin in the entry-table entry (located by PC-number translation), with six binary zeros appended on the right, are loaded into bits 33-63 of control register 5. Thus, the ASTE in the entry-table entry becomes the new primary ASTE. If a subsequent PC instruction is executed, its PC-number translation will use the linkage-table origin (or linkage-first-table origin) from the primary ASTE for any PC-number translation operations.

That wraps it up for a basic program call, that is, a PROGRAM CALL that does not use the linkage stack. (Recall, whether or not a PC is basic or stacking is determined by the T bit, bit 0 of byte 16 in the entry-table entry.)

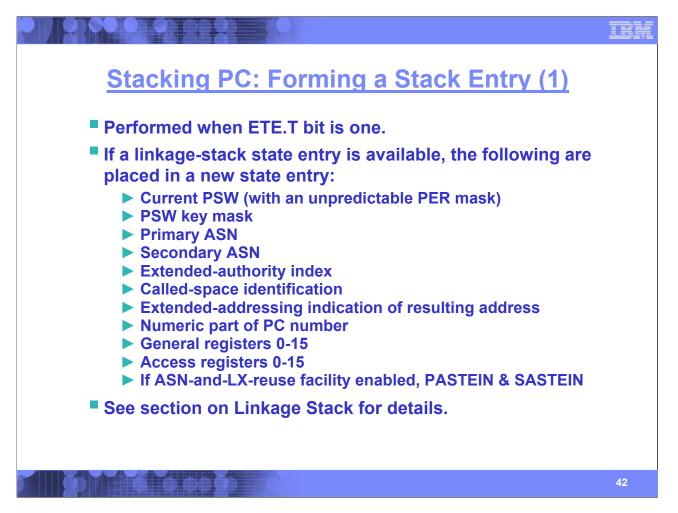

Here we get into a chicken-and-egg problem. In order to describe the operation of a stacking PC, some understanding of the linkage stack must creep in, even though we don't get to the details until around slide 64.

A stacking program call saves all of the program's current state information in a linkage-stack state entry, the details of which come later.

Because all of the relevant program-context information is saved in a stack entry, the stacking PC does not save program state information in general registers 3 and 14 (as is done in a basic PC).

Stacking PC also provides more flexible program controls.

- 1. Basic PC provides no means of manipulating the PSW key. Stacking PC allows the PSW key to remain unchanged, or provides a means of replacing the PSW key.

- 2. With basic PC, each subsequent (nested) PC causes the PSW key mask (PKM) to either remain the same or increase its level of key authorization. This is because the entry key mask in the ETE is logically ORed with the PKM in CR3. With stacking PC, the PKM may be either ORed with the EKM (as in basic PC), or the PKM may be completely replaced by the value of the ETE EKM. Thus, with a stacking PC, the level of PKM authorization may be decreased as the program progresses.

- 3. An extended-authorization index (EAX) in control register 8 is used by the stacking PC operation and by access-register translation (ART). Stacking PC allows the EAX to be optionally modified.

- 4. Finally, a routine called by basic PC retains the address-space control of the caller. Stacking PC allows the called routine to receive control in either the primary- or the AR-mode.

A stacking PC is performed whenever the T bit (bit 0 of byte 16 in the entry table) is one.

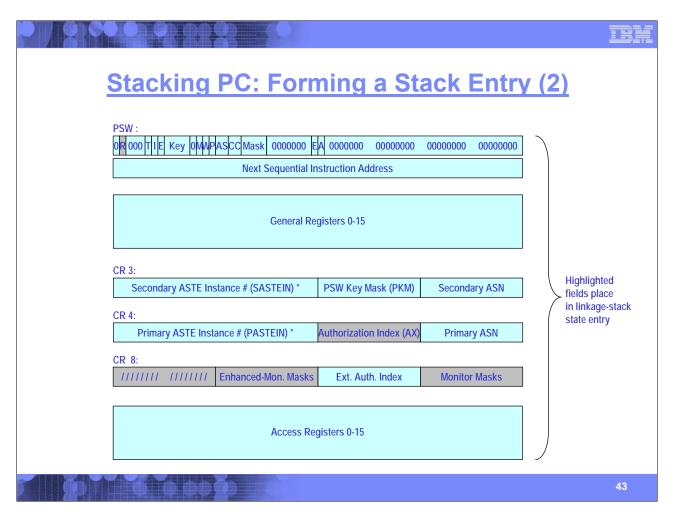

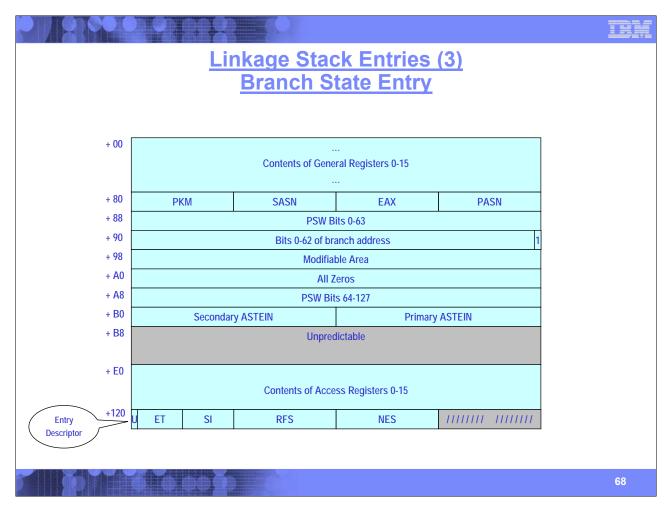

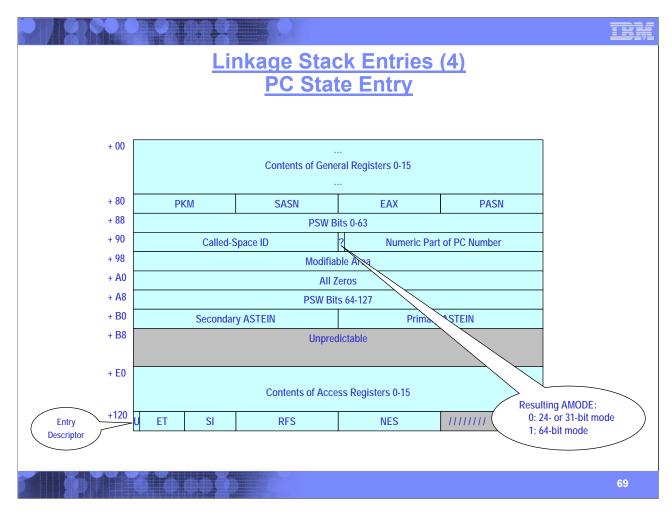

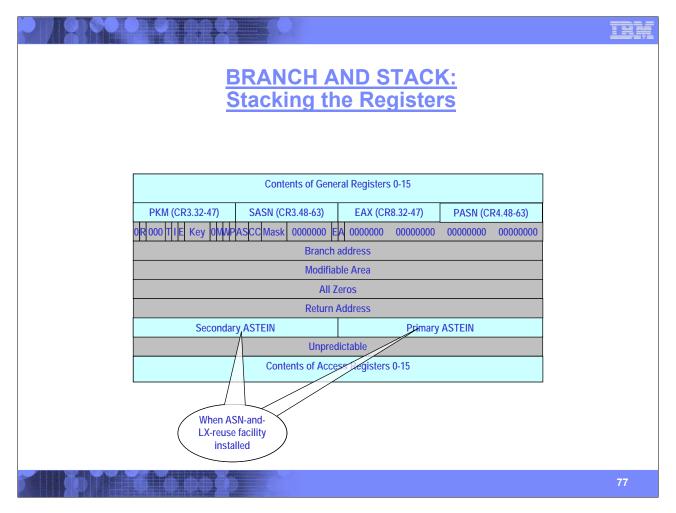

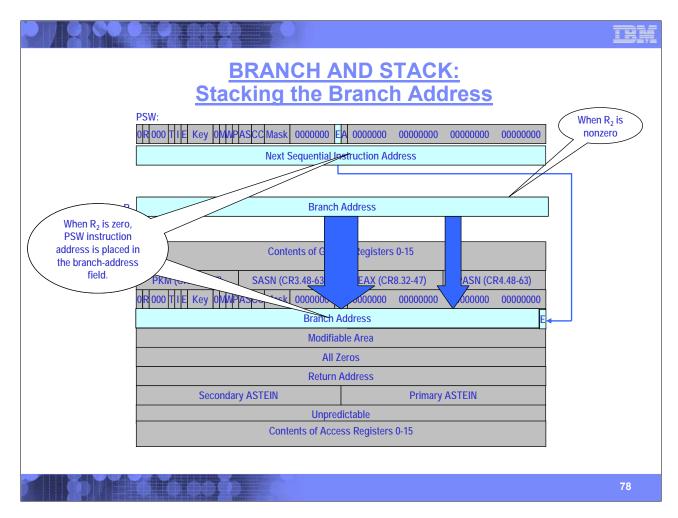

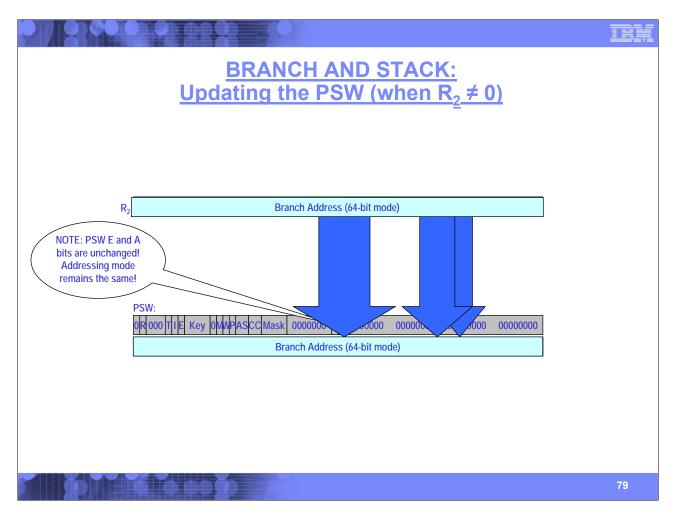

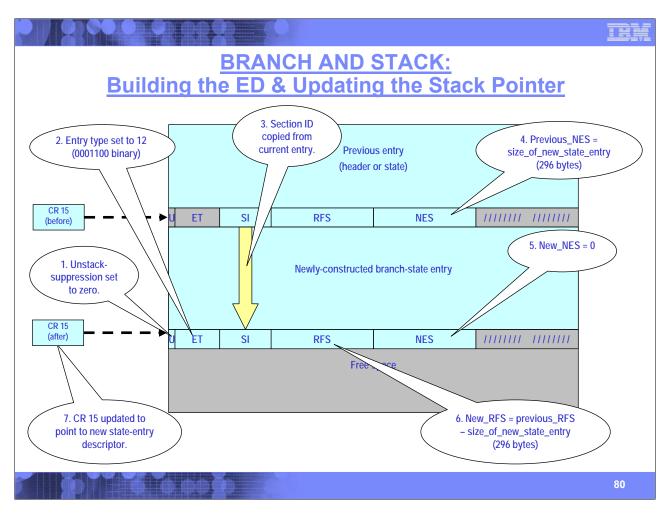

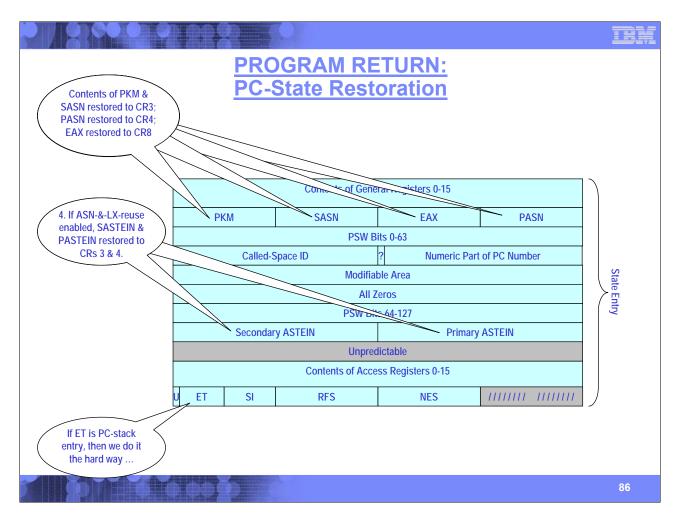

Assuming that there is space in the linkage stack, the information listed on this slide is preserved in a new PC-state linkage-stack entry. We'll see a lot more detail on these fields later in the linkage-stack discussion.

To restate the material on the previous foil in graphic terms, the fields illustrated on this slide and the next slide are stored in a PC-state linkage-stack entry.

This slide shows the basic register fields that are stored in a PC-state entry.

|    | tacking P                                                            | C: Form              | ning a St                       | ack Entr                                | <b>IB</b>                |  |  |

|----|----------------------------------------------------------------------|----------------------|---------------------------------|-----------------------------------------|--------------------------|--|--|

|    | try-Table Entry                                                      |                      |                                 |                                         |                          |  |  |

|    |                                                                      | Entry Instruction    |                                 | P                                       |                          |  |  |

| A  |                                                                      |                      | Entry Key Mask (EKM)            | /////////////////////////////////////// |                          |  |  |

| TG |                                                                      | try Ext. Auth. Index | / Address Space 2 <sup>nd</sup> | <b>y</b>                                |                          |  |  |

|    |                                                                      |                      | Entry Pa                        | irameter                                |                          |  |  |

|    |                                                                      |                      | Numeric part                    | of PC number                            | Highlighted fields place |  |  |

| AS | SN-Second Table (ASTE)                                               |                      |                                 |                                         | in linkage-stack         |  |  |

| I  | Authority-Table                                                      | Origin / B           | Authorization Index             | Auth. Table Length CR                   | state entry.             |  |  |

|    | Address-Space Control Element (ASCE) ASN and bits<br>16-32 of ASTEIN |                      |                                 |                                         |                          |  |  |

| /  | Primary-Space Access-Lis                                             | st Origin ALL        | ASTE Seque                      | nce Number                              | are the Called-          |  |  |

| V  | Linkage-Table Origi                                                  |                      | Available for I                 | Programming                             | Space ID (CSI)           |  |  |

| _  | Available for Programming                                            |                      |                                 |                                         |                          |  |  |

| 1  |                                                                      | Rese                 | ASTE Instan                     | ce Number                               |                          |  |  |

|    |                                                                      |                      |                                 |                                         |                          |  |  |

|    |                                                                      | I J                  |                                 |                                         |                          |  |  |

|    |                                                                      |                      |                                 |                                         | )                        |  |  |

|    |                                                                      |                      |                                 |                                         |                          |  |  |

|    |                                                                      |                      |                                 |                                         | 44                       |  |  |

This slide shows additional fields stored in a PC-state entry.

Note: The PC number is not required in order to return from a stacking program call. Rather, it provides diagnostic information in the stack entry; should the task abnormally terminate, the PC number can be inspected in the dump of the linkage stack.

The called-space ID (CSI) in the linkage stack is an interesting compromise. It includes the ASN from the entry-table entry and half of the ASTE instance number. Again, the ASTE instance number in the CSI is used for diagnostic purposes only.

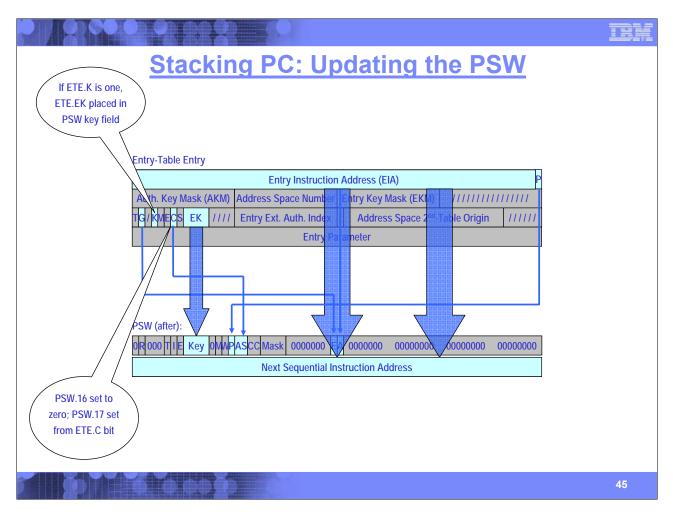

During the execution of a stacking PC, the new PSW (which receives control when the instruction completes) is constructed as follows:

[CLICK] The G bit in the entry-table entry (bit 1 of byte 16) becomes the new extended-addressing control in bit 31 of the PSW. Note, this differs from basic PC which could not change the extended-addressing mode.

[CLICK] When the G bit is zero (i.e., 24- or 31-bit addressing mode\_, bits 33-62 of the entry-instruction address field, with a binary zero appended on the right, become bits 33-63 of the PSW instruction address (actually, bits 97-127 of the PSW). Bit 32 of the EIA becomes the new basic-addressing-mode bit in bit 32 of the PSW.

[CLICK] When the G bit is one, (i.e., 64-bit addressing mode), bits 0-62 of the EIA field, with a binary zero on the right, becomes the new PSW instruction address (bits 64-127 of the PSW).

[CLICK] Bit 63 of the EIA becomes the new problem-state bit, bit 15 of the PSW.

[CLICK] If the K bit in the ETE (bit 3 of byte 16) is one, then the entry key in bits 0-3 of byte 117 of the ETE becomes the new PSW key (bits 8-11). If the K bit is zero, the PSW key is unchanged.

[CLICK] Recall that the called routine can receive control in either the primary- or the AR mode. In the primary-space mode, the addressspace-control bits of the PSW (bits 16-17) are 00 binary, whereas in the AR mode, PSW bits 16-17 are 01 binary. Thus, stacking PC sets PSW bit 16 to zero, and sets PSW bit 17 to the contents of the C bit of the ETE (bit 6 of byte 16).

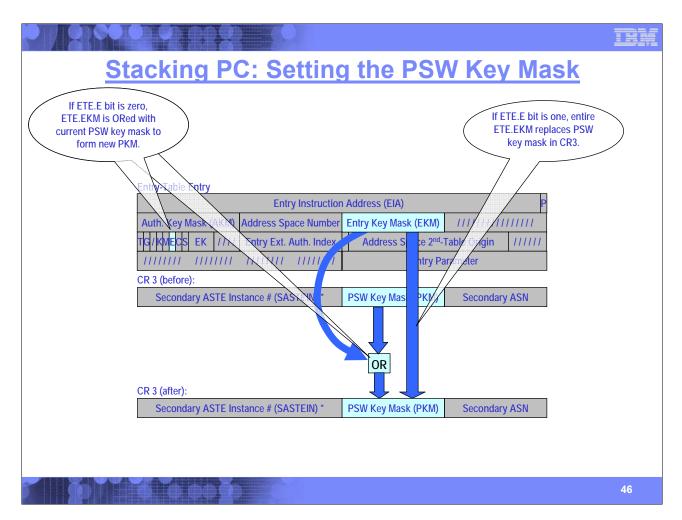

The setting of the PSW key mask is handled next.

[CLICK] If the E bit of the ETE (bit 5 of byte 16) is zero, then the entry-key mask (EKM) in bytes 12-13 of the ETE is logically ORed with the PSW key mask in bits 32-47 of control register 3 (as is done in a basic PC).

[CLICK] If the E bit is one, then the entire EKM in the ETE replaces the PKM in CR3.

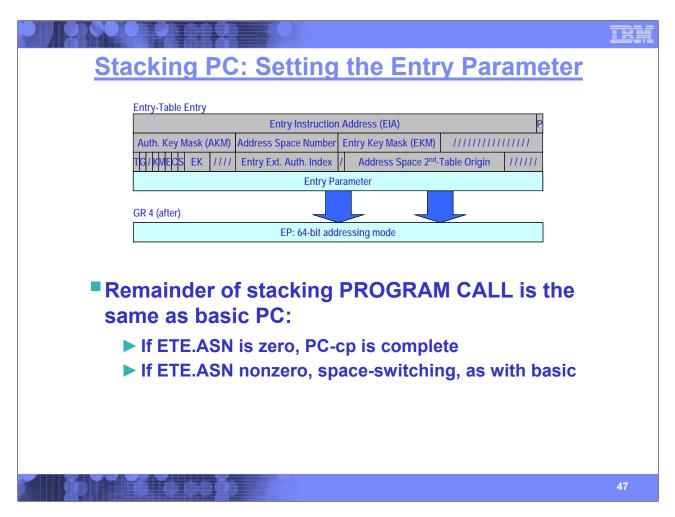

As with basic PC, the stacking PC places the entry parameter in the ETE into general register 4.

[CLICK] If the called routine is in either the 24- or 31-bit addressing mode (as indicated by the G bit of the ETE), then bits 32-63 of the entry parameter are placed into the corresponding bits of general register 4.

[CLICK] If the called routine is in the 64-bit addressing mode, then the entire entry parameter is placed into bits 0-63 of GR4.

[CLICK] The remainder of a stacking PC is the same as a basic PC: If the ASN in the ETE is zero, then it's a current-primary PC, and execution is complete. If the ETE ASN field is nonzero, then space-switch processing occurs, as previously discussed.

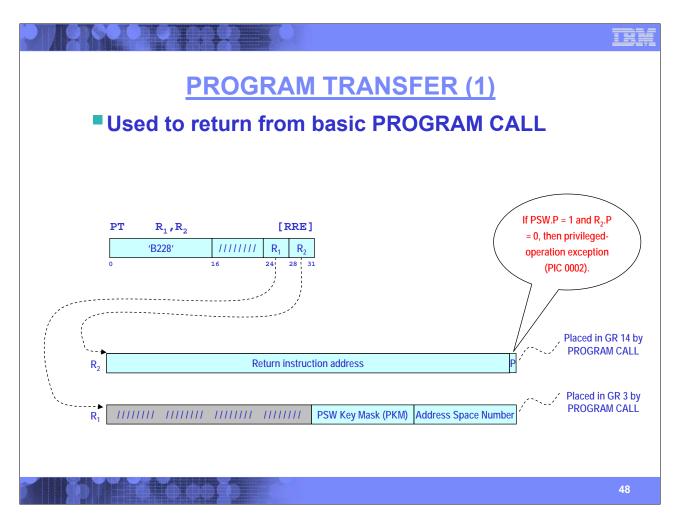

PROGRAM TRANSFER was the original mechanism used to return from a PROGRAM CALL.

[CLICK] The first-operand register contains the PKM and ASN to be restored. In most circumstances, these values are the fields placed into general register 3 by a basic PC.

**[CLICK]** The second-operand register contains the return instruction address and problem-state bit to be restored. In most circumstances, these values are the fields placed into general register 14 by a basic PC. In this illustration a 24- or 31-bit address is being restored, determined by the A bit in bit 32 of the second-operand register.

[CLICK] Here we see a 64-bit address in the second-operand register, with the P bit on the right.

**[CLICK]** The enquiring mind may notice that the called program is given control over various authorization states: the P bit and the PKM. The devious mind may attempt to alter set these bits to provide greater authority, and then simply execute a PROGRAM TRANSFER. As shown in the call-out balloon, if the program is in the problem state, but attempts to set the PSW P bit to zero (requesting supervisor state), a privileged-operation exception is recognized (PIC 0002 hex).

[CLICK] With the advent of the advanced-space facilities, PROGRAM TRANSFER is intended for returning from a basic PROGRAM CALL. A new instruction, PROGRAM RETURN (PR), is used to return from a stacking PC. PR will be discussed later.

Note, with the advent of the ASN-and-LX-reuse facility, there is also a PROGRAM TRANSFER WITH INSTANCE (PTI) instruction. Execution of this instruction is similar to PC, but with additional instance-number checking. This presentation does not discuss PTI further. See the *z*/Architecture Principles of Operation for further details on PTI.

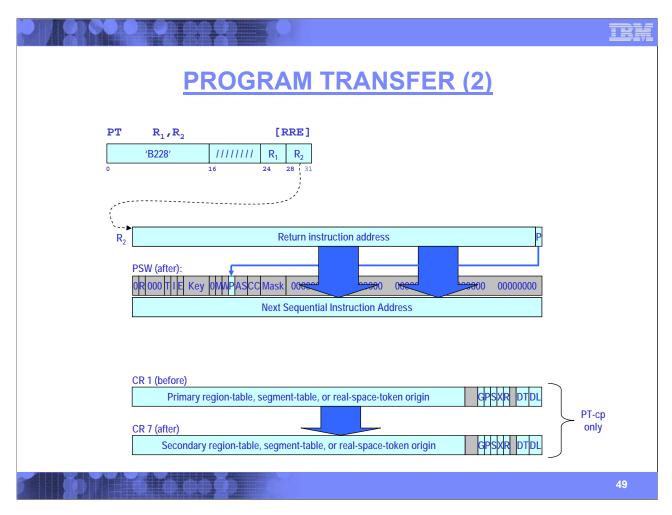

[CLICK] In the 24- or 31-bit addressing mode, bit 32 of the second-operand register becomes the new basic-addressing-mode bit in the PSW (PSW bit 32), and bits 33-62 of the second-operand register, with a binary zero appended on the right, become bits 33-63 of the PSW instruction address (bits 97-127 of the PSW).

[CLICK] In the 64-bit addressing mode, bits 0-62 of the second-operand register, with a binary zero appended on the right replace the entire PSW instruction address (bits 64-127 of the PSW).

Regardless of 24/31 or 64-bit addressing mode, bit 63 of the second-operand register becomes the new problem-state bit, bit 15 of the PSW.

[CLICK] In a subsequent slide, we'll see the difference between a current-primary PROGRAM TRANSFER (PT-cp) and a spaceswitching PROGRAM TRANSFER (PT-ss). For the PT-cp, the contents of the primary address-space-control element (P-ASCE) in control register 1 is copied to the secondary ASCE in control register 7.

This slide shows the restoration of the PSW key maskm secondary address-space number, and, when applicable, the secondary ASTE instance number.

[CLICK] The address-space number in bits 48-63 of the first-operand register are loaded into the corresponding bits of control register 3, becoming the new secondary ASN.

**[CLICK]** A reverse of the PKM process done in PROGRAM CALL is performed: The PSW key mask in bits 32-47 of the first-operand register are logically ANDed with the PKM in bits 32-47 of control register 3; the result replaces the PKM in CR3. Thus, the resulting PSW key mask will either remain the same, or have reduced authorization.

[CLICK] If the ASN-and-LX-reuse facility is enabled, the primary ASTE instance number in bits 0-31 of control register 4 is copied to the secondary ASTEIN in the corresponding bits of control register 3.

**[CLICK]** If the address-space number in the first-operand register is equal to the primary ASN in CR4, then this is a current-primary PROGRAM TRANSFER (PT-cp), and execution is complete. Otherwise, this is a space-switching PROGRAM TRANSFER (PT-ss), and execution continues with ASN translation on the following slides.

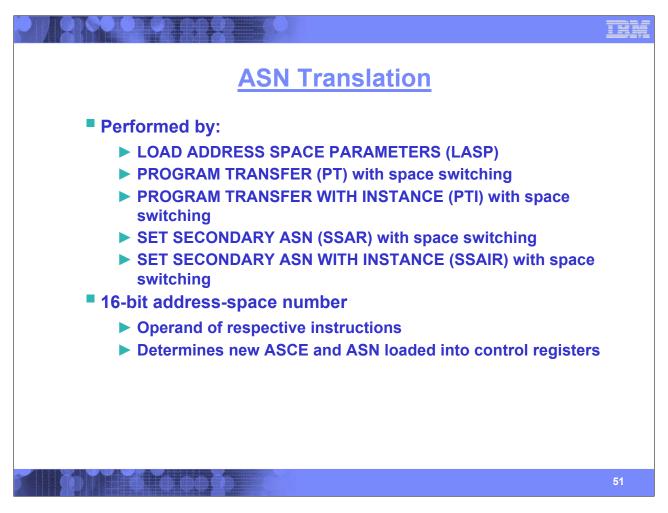

In a space-switching PROGRAM CALL, the new ASN is in the ETE (which is controlled by the OS). In the case of certain instructions such as a space-switching PROGRAM TRANSFER (and the others listed on this slide), the program supplies an address-space number as an operand in a register or in a storage location. Being program supplied – perhaps by an application program -- the ASN supplied to PT cannot be trusted to be authorized for use by the program.

The ASN-translation process is a means by which the 16-bit ASN provided by these instructions can be used to locate control structures provided by the operating system that (a) determine authorization, and (b) provide context information on the corresponding address space.

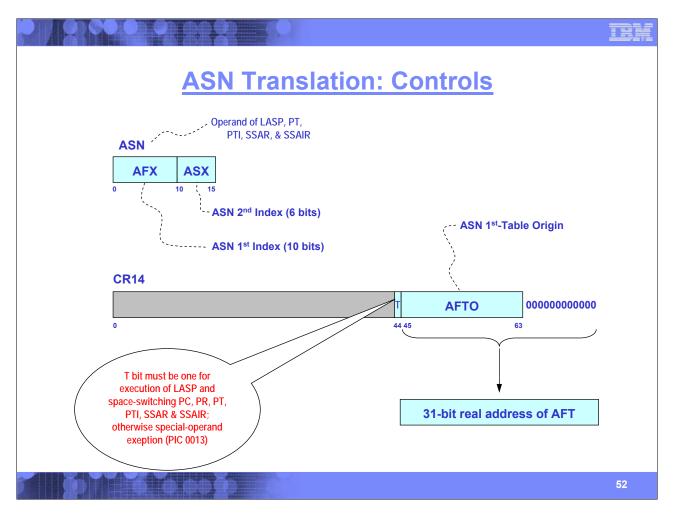

Inputs to ASN translation are the ASN and two fields in control register 14.

[CLICK] The ASN is an operand of the LASP, PT, PTI, SSAR, and SSAIR instructions. As with many other fields used by the hardware, it is split into multiple index fields

[CLICK] The ASN first index (AFX) is in bits 0-9 of the ASN

[CLICK] The ASN second index (ASX) is in bits 10-15 of the ASN.

**[CLICK]** Bit 44 of control register 14 is the ASN-translation control (T). The T bit must be 1 in order for space-switching forms of PC, PR, PT, PTI, SSAR, and SSAIR to be executed. If the T bit is zero when these instructions are executed, a special-operation exception (PIC 0013 hex) is recognized – regardless of whether the CPU is in the problem or supervisor state.

[CLICK] Bits 45-63 of control register 14 contain the ASN first-table origin (AFTO). The AFTO, appended on the right with 12 binary zeros, forms the 31-bit real address of the ASN first table (AFT).

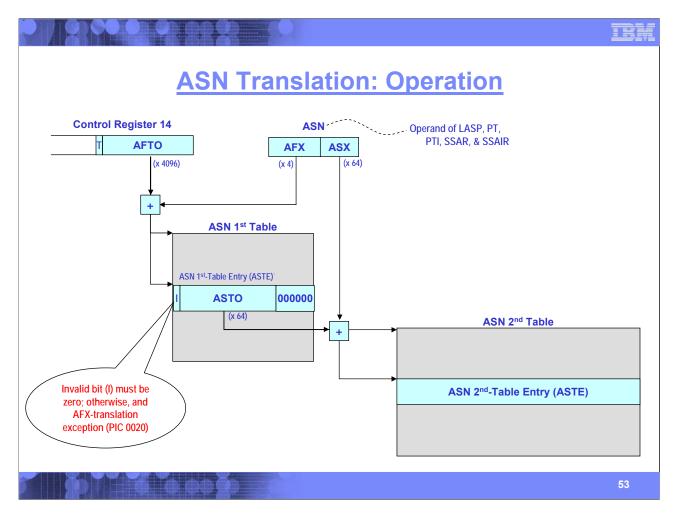

As shown on the preceding slide, the givens to ASN translation are the ASN (from one of the instructions that cause ASN translation) and the ASN-first-table origin (AFTO) in control register 14.

[CLICK] The AFTO, multiplied by 4,096, points to the first byte of the ASN first table (AFT).

[CLICK] The ASN first index (AFX, bits 0-9 of the ASN), multiplied by 4, are added to the AFTO to locate an ASN-first-table entry (AFTE).

[CLICK] Bit 0 of the AFTE is the invalid bit. This bit must be zero, otherwise an AFX-translation exception is recognized (PIC 0020 hex).

[CLICK] If the AFTE is valid, bits 1-25 of the entry, appended on the right with six binary zeros, form the 31-bit real address of the ASN second table (AST).

[CLICK] The ASN second index, bits 10-15 of the ASN, multiplied by 64, form the address of an ASN second table entry (ASTE). This ASTE is the result of ASN translation.

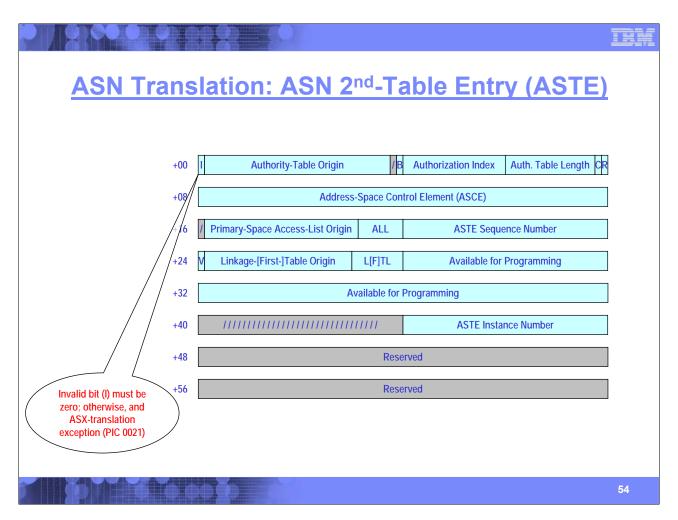

This slide shows the contents of the ASN second-table entry (ASTE).

[CLICK] Bit 0 of the ASTE is the invalid bit. When an ASTE is the result of ASN translation, the invalid bit must be zero; otherwise, an ASX-translation exception is recognized (PIC 0021 hex).

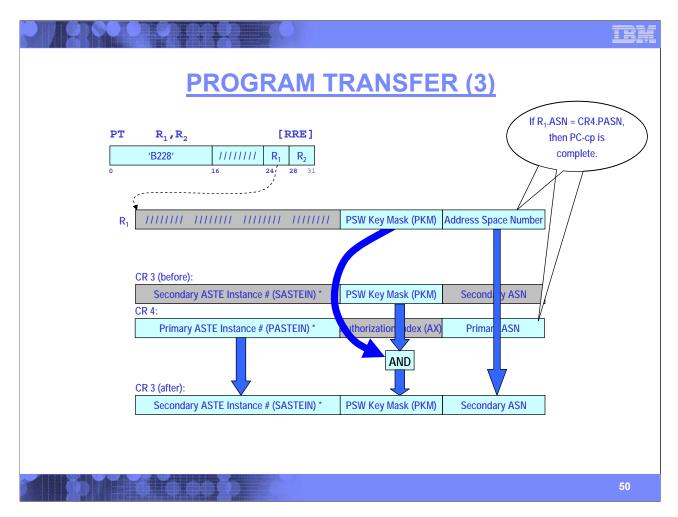

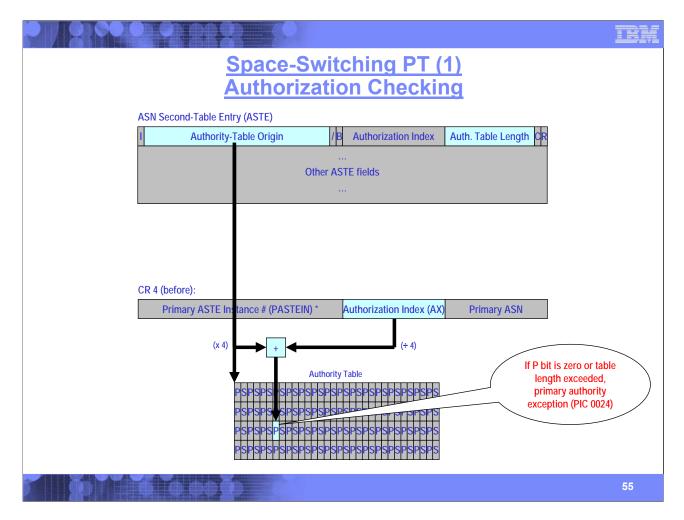

Following ASN translation, the next part of PROGRAM TRANSFER execution is determining whether the program is authorized to use the designated ASTE.

**[CLICK]** Bits 1-29 of the ASTE located by ASN translation, appended on the right with two binary zeros, forms the 31-bit real address of an authority table. The authority table is comprised of pairs of primary- and secondary-authorization bits (P and S), four pairs per byte.

[CLICK] The authorization index (AX) in bits 32-47 of control register 4, divided by four, is used to locate a pair of P/S bits in the authority table. The pair of bits within the byte is identified by the remainder of the division of the AX and four.

**[CLICK]** If the AX exceeds the length of the authority table (as indicated by the authority-table length in bits 48-61 of the ASTE), or if the designated primary-space (P) bit in the authority table is zero, then a primary-authority exception is recognized (PIC 0024 hex).

Assuming that the program is authorized to switch to this primary ASN (see previous slide), the following occurs:

[CLICK] The address-space number in bits 48-63 of the first-operand register is placed into the corresponding bits of control register 4.

[CLICK] The authorization index in bytes 4-5 of the ASTE (located by ASN translation) is placed into bits 32-47 of control register 4.

[CLICK] When the ASN-and-LX-reuse facility is enabled, the ASTE instance number in bytes 44-47 of the ASTE are placed in both the primary and secondary ASTEIN fields in control registers 4 and 3, respectively.

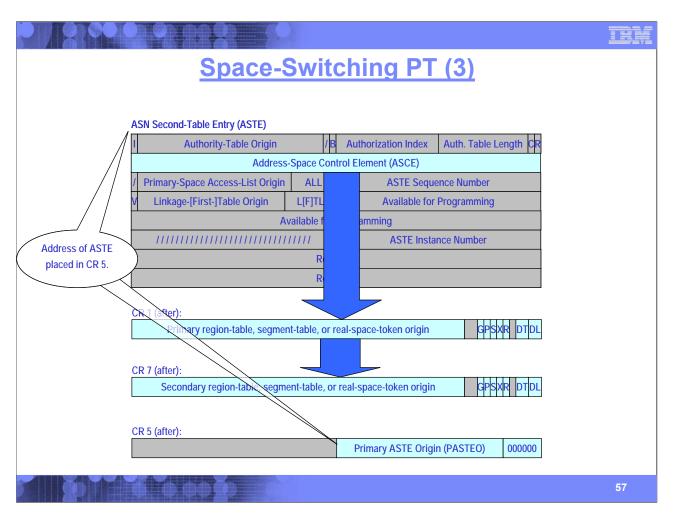

The final operations in a space-switching PROGRAM TRANSFER are as follows:

[CLICK] The address-space control element (ASCE) in bytes 8-15 of the ASCE (located by ASN translation) is placed into both the primary and secondary ASCE fields in control registers 1 and 7, respectively.

[CLICK] The address of the ASTE (located by ASN translation) is placed into control register 5, becoming the new primary ASTE origin (PASTEO).

This completes the execution of a space-switching PROGRAM TRANSFER.

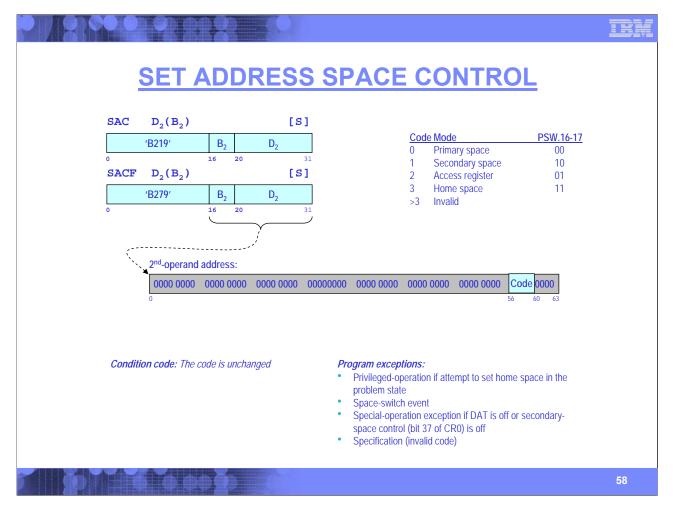

SET ADDRESS SPACE CONTROL (SAC) and SET ADDRESS SPACE CONTROL FAST (SACF) are both used to set the addressing mode in bits 16-17 of the PSW.

[CLICK] The storage operand of these instructions is not used to access storage.

[CLICK] Rather, bits 56-59 of the operand address form a code that is used to determine the setting of address-space control bits in the PSW, as shown.

The primary difference between SAC and SACF are that SAC performs a serialization and checkpoint-synchronization operation before begins and after the operation completes; SACF performs neither serialization nor checkpoint synchronization. Additionally, it is unpredictable whether SACF checks the secondary-space control in bit 37 of CR0.

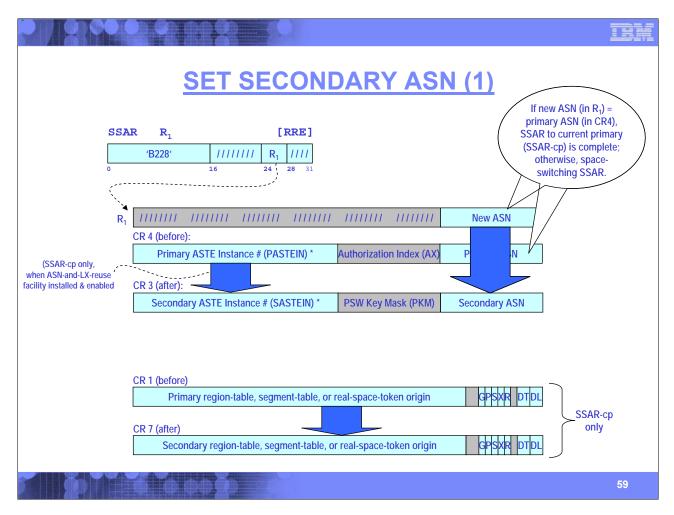

The SET SECONDARY ASN (SSAR) instruction allows the program to switch secondary address spaces – without having to call a separate routine as with PROGRAM CALL. However, similar processes to PC are performed.

[CLICK] The first-operand register contains a new secondary ASN in bits 48-63. The new ASN is copied to the secondary-ASN field in bits 48-63 of control register 3.

[CLICK] For a SSAR to the current-primary address space, the primary address-space control element (P-ASCE) in control register 1 is copied to the secondary ASCE in control register 7. We'll see how the current-primary or space-switching determination is made in a moment.

[CLICK] If the ASN-and-LX-reuse facility is installed, the primary ASTE instance number (PASTEIN) in bits 0-31 of control register 4 is copied to the secondary ASTEIN (in the corresponding bits of control register 3).

[CLICK] If the new ASN in the first-operand register is equal to the primary ASN in bits 48-63 of control register 4, then this is a SET SE CONDRAY ASN to the current primary (SSAR-cp), and execution is complete. Otherwise, this is a space-switching SSAR (SSAR-ss), and processing continues as described on the following slides.

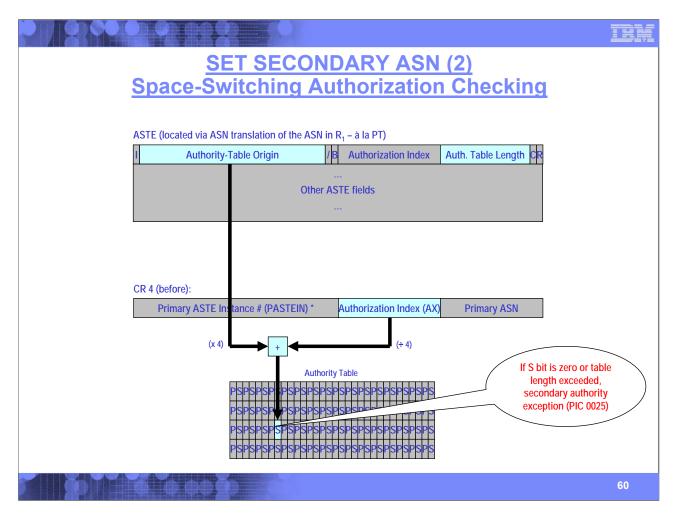

For a space-switching SSAR, the designated ASN is translated, as described in operation of PROGRAM TRANSFER. If ASN-translation is successful, a new secondary ASTE is located.

ASN authorization proceeds in a manner similar to that of PROGRAM TRANSFER, except that a secondary-authority bit (the second bit in the P/S pair of bits) is examined.

[CLICK] If the authorization index in bits 32-47 of control register 4 exceeds the length of the authority table (in bits 48-61 of the ASTE located by ASN translation), or if the S bit designated by the AX is zero, then a secondary-authority exception is recognized (PIC 0025 hex)

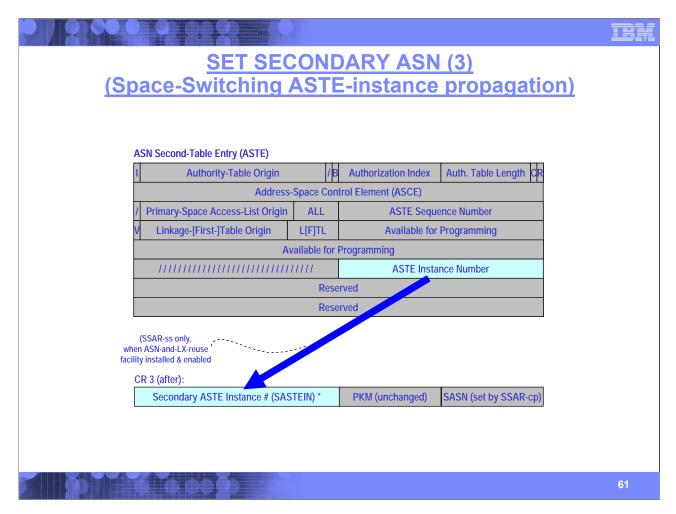

Back on slide 50, we showed that for SSAR-cp, the primary ASTE instance number in CR4 was copied into the secondary ASTE instance number in CR3 when the ASN-and-LX-reuse facility is enabled.

[CLICK] For a space-switching SSAR, the ASTE instance number in the ASTE (located by ASN translation) is placed into the secondary ASTE instance number when ALRF is enabled.

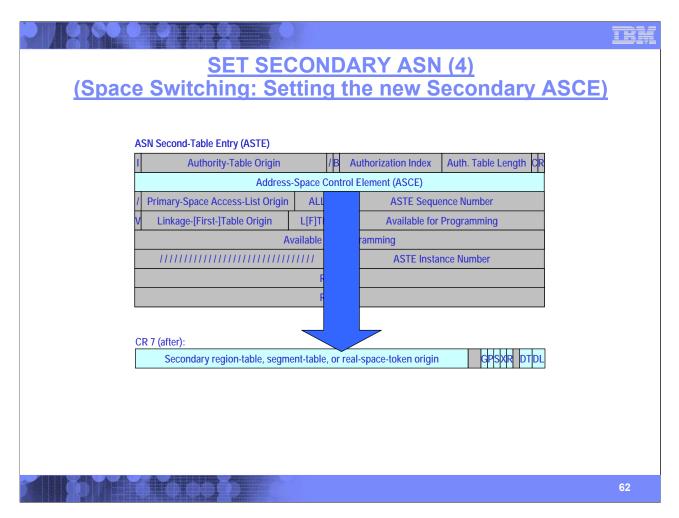

The final operation in a space-switching SSAR is to load the new secondary ASCE:

[CLICK] The ASCE field in bytes 8-15 of the ASTE (located by ASN translation) is loaded into the secondary ASCE in control register 7

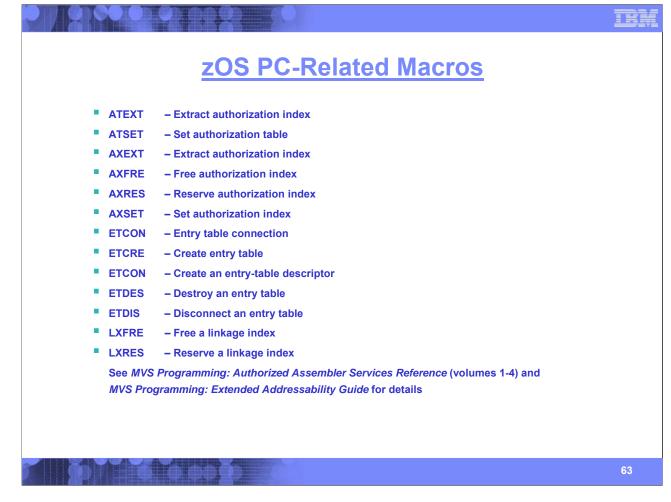

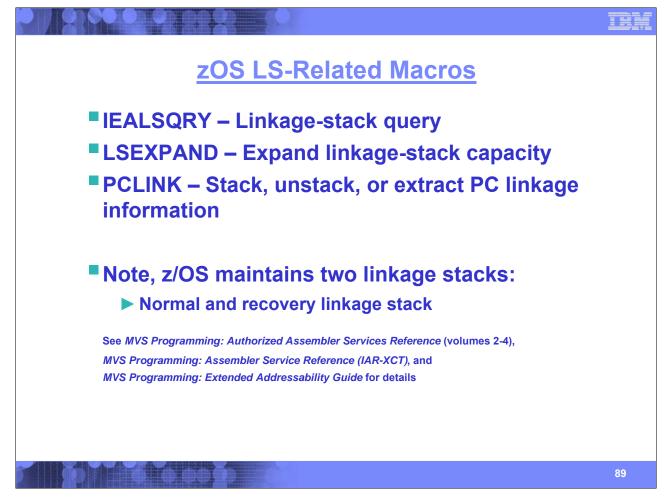

z/OS provides a robust suite of macro instructions for the construction and management of the various hardware tables used in a dualaddress-space environment. This slide provides an inventory of some of these macro instructions.

For more details, please refer to the following documents:

- zOS MVS Programming: Authorized Assembler Services Reference, Volume 1 (ALE-DYN) [SA22-7609]

- zOS MVS Programming: Authorized Assembler Services Reference, Volume 2 (EDT-IXG) [SA22-7610]

- zOS MVS Programming: Authorized Assembler Services Reference, Volume 3 (LLA-SDU) [SA22-7611]

- zOS MVS Programming: Authorized Assembler Services Reference, Volume 4 (SET-WTO) [SA22-7612]

- zOS MVS Programming: Extended Addressability Guide [SA22-7614]

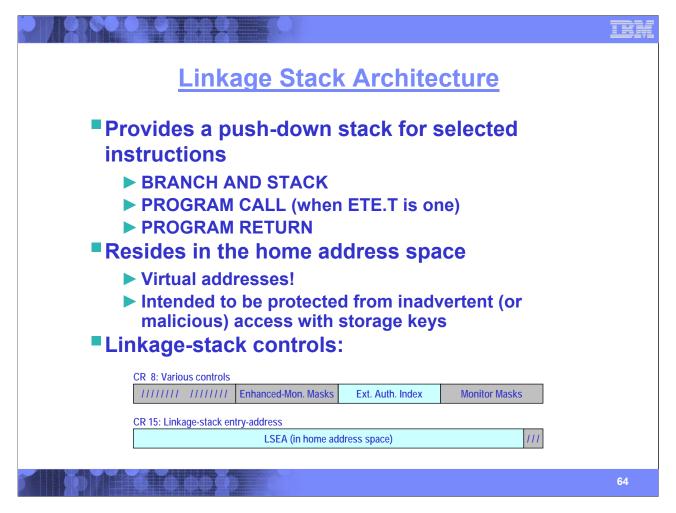

The linkage-stack architecture was added as a component of the advanced-space facilities (ASF) in 1989.

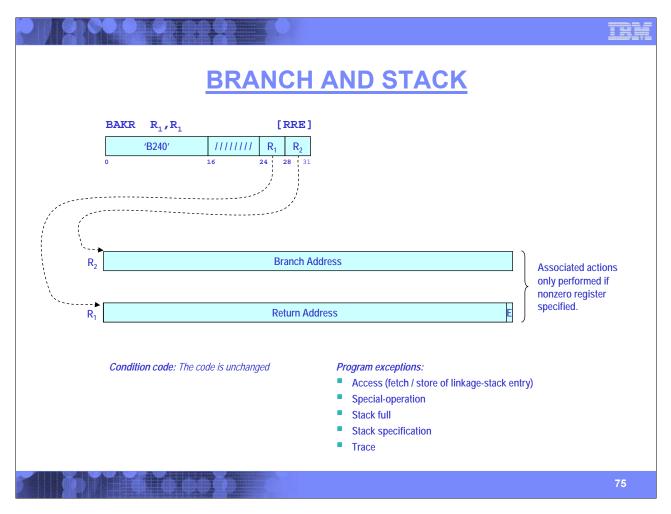

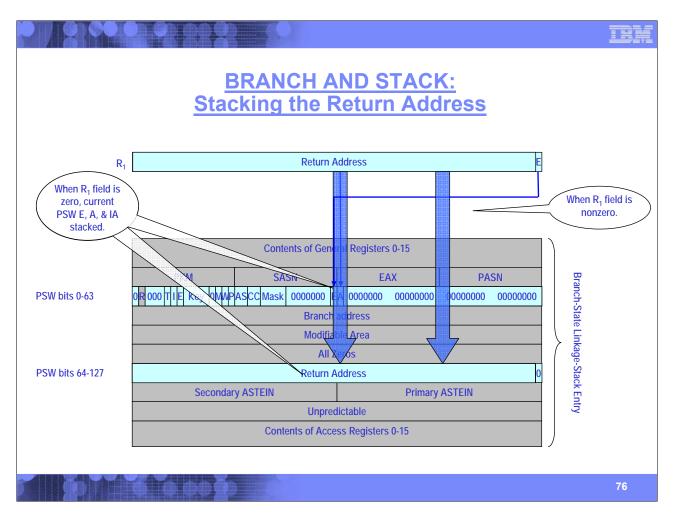

Somehow S/360 and its progeny managed to evade having a push-down stack for 25 years, but with the advent of ASF, a specialized, highly-structured stacking mechanism was added. This stack is used for only three instructions. Two instructions are used to call a program: BRANCH AND STACK (new with ASF), and PROGRAM CALL (modified with ASF). The third instruction, PROGRAM RETURN, provides a means of returning from either BRANCH AND STACK or a stacking PROGRAM CALL.

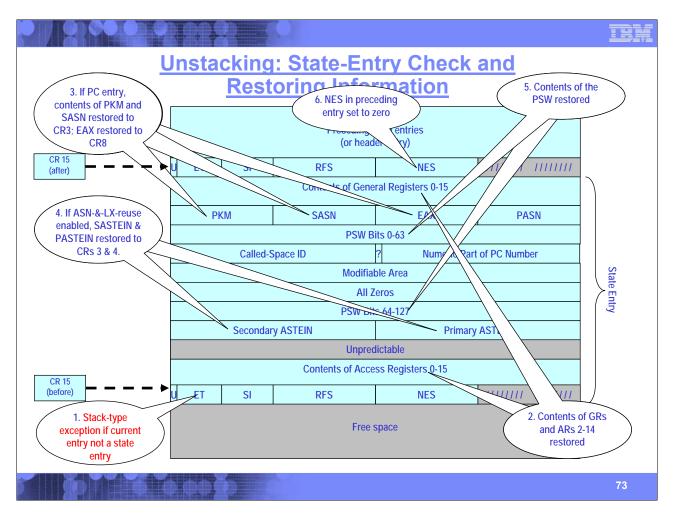

Unlike many of the hardware structures described thus far (which reside in real storage) the linkage stack lives in the home address space – along with other task-related structures. To ensure that the linkage stack is not inadvertently – or maliciously – accessed by unauthorized programs, it is intended to reside in storage that is protected by storage-protection keys ... specifically, fetch protected.