# IBM z/Architecture CPU Features A Historical Perspective

Dan Greiner

dgreiner@us.ibm.com

z/Server Architecture

SHARE 116 in Anaheim

Session 8635, 1 March 2011, 11:00 am

**IBM Systems and Technology Group (STG)**

© Copyright International Business Machines Corporation 2011.

### The Legal Stuff

#### **Trademarks:**

- The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

- ESA/390

- IBM

- z/Architecture

- z/OS

- z/VM

- IEEE is a trademark of the Institute of Electrical and Electronics Engineers, Inc. in the United States, other countries, or both.

- Linux is a registered trademark of Linus Torvalds in the United States, other countries or both.

- Unicode is a registered trademark of Unicode, Incorporated in the United States, other countries, or both.

- Other trademarks and registered trademarks are the properties of their respective companies.

- All information contained in this document is subject to change without notice. The products described in this document are not intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

- While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

- The information in contained in this document is provided on an "AS IS" basis. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document. Copyright International Business Machines Corporation 2011. Permission is granted to SHARE, Inc. to

- publish this presentation in the proceedings of SHARE 116.

- A brief history of the CPU architecture leading up to System Z

- Facilities added since the introduction of z/Architecture in 2000

- > z900 (2064) and z800 (2066):

- > z990 (2084) and z890 (2086):

- > z9-109 EC (2094) and z9-109 BC (2096)

- > z10 EC (2097) and z10 BC (2098)

- > z196 (2817)

- Why the new facilities were implemented

- Mostly CPU facilities discussed, not I/O

This presentation will review new CPU facilities that have been added to z/Architecture since its introduction in 2000.

The facilities will be reviewed in (semi) chronological order of introduction, based on the availability of new machine levels.

This presentation deals mostly with CPU facilities ... not I/O.

The presentation does not go into bit-level detail of each new instruction. Rather, the presentation attempts to explain why the various facilities were introduced, and how a program might go about exploiting them.

Please refer to my past SHARE presentations on the z9, z10, and z196 for a more detailed description of the recent additions to z/Architecture, or, refer to the most recent z/Architecture Principles of Operation (SA22-7832-08).

- Provided 32-bit arithmetic

- ► 16 general-purpose registers

- Provided 24-bit addressing (16 megabytes max.)

- ► Real addressing only! No virtual memory

- ► More than a few megabytes was quite rare

- Approximately 141 instructions total

- Some features were optional

- Floating point (with 4 floating-point registers)

- Decimal instructions (in-storage only)

- Direct control

- Protection feature (i.e., storage keys)

- I/O subsystem provided a maximum of 7 channels

- Limited by mask bits in the PSW.

Nearly 50 years ago, IBM introduced the System 360 series of processors, providing a common architecture across all models of the product line.

The basic characteristics of the architecture are shown on this slide:

- 32-bit arithmetic using a set of sixteen 32-bit general registers.

- 24-bit real storage addressing, providing support for up to 16 megabytes of main storage. Although seemingly small by 2011 standards, in 1964, 16 megabytes was mind-bogglingly huge ... at approximately \$1.00 per byte, this was far more than most customers could afford, and physically it would have required hundreds of square feet of costly raised-floor space in the machine room.

Also recall that the original S/360 did not include dynamic address translation (DAT), thus there was no virtual memory. This necessitated a very frugal approach to programming (which seems to have fallen out of fashion in contemporary programming languages), and required some rather awkward programming conventions such as overlays.

The initial *IBM System/360 Principles of Operation* (A22-6821-0) described 141 instructions, however many of these instructions represented optional features in the original machines. One of the features that made the architecture superbly reliable – that of storage-protection keys – was optional in the original S/360!

The number of I/O channels was limited by interruption-enablement bits in the program-status word (PSW): one byte-multiplexer channel (to which unit-record devices such as card readers, punches, printers, and terminals were attached), and up to six selector channels (to which disk and tape devices were attached).

- Provided virtual addressing

- ► One or multiple 24-bit virtual spaces

- ► Still limited to 24-bit real storage addressing

- Introduced new 16 control registers

- Introduced 13 new instructions

- ► Load/store control

- ► Compare / move long

- ► Compare / insert / store character under mask

- ▶ &c.

- I/O subsystem expanded to (up to) 16 channels

- **▶** 32 channel option on some machines

- Program-event recording

H

In 1971, IBM introduced the System 370, continuing the instruction set from the original S/360 (and making many of the optional features standard).

The S/370 added virtual addressing, providing 24-bit addressability which allowed up to 16 megabytes of virtual memory to be accessed with no special tricks required by the application program. Initially, IBM's Single Virtual Storage (SVS) operating system provided a single 16 M-byte virtual space, however soon thereafter, the Multiple Virtual Storage (MVS) operating system provided many 16 M-byte virtual spaces. The CPU was still limited to 24-bit real addresses, thus the maximum amount of real memory still remained 16 M-bytes or less ... again, most customers had far less real storage.

One of the initial advantages of virtual storage was the ability to over-commit real storage ... potentially stuffing hundreds of megabytes of virtual data into a 16 M-byte (maximum) bag. However, as real storage has become increasingly more affordable over the years (decades, actually), over-committing real storage is of less importance ... and many z/OS sites perform very little paging.

The S/360's storage-protection key feature allowed the segregation of data in real storage into one of 16 classes, the access to which was enforced by the hardware. Although a bane to novice programmers who encounter unexpected protection exceptions (that is, a program-interruption code 0004, which z/OS and its predecessors translate into an S-0C4 abend code), the storage-protection keys are one of the features that contribute to the architecture's incredible reliability. Virtual storage – and the ability to segregate data into any number of separate address spaces – is another feature that operating systems can exploit to increase reliability.

To implement virtual storage – and several other features – the architecture introduces 16 new control registers that could be directly manipulated by the control program. This gave the control program much more flexibility in the control of the machine, the virtual context, the enablement of I/O operations (now supporting up to 16 channels), and other new features such as program-event recording (PER).

The S/370 also introduced several new instructions ... many of which were used by the control program to manage the hardware, but some of which became instant favorites: MOVE LONG and COMPARE LOGICAL LONG, to name a few. However, you will notice that there were relatively few new instructions (at least, relative to the last decade).

### **System 370 Enhancements (1978-1982)**

- 26-bit real addressing

- ► Virtual address space still limited to 24 bits (16 MB)

- Various MVS-assist instructions

- ▶ Instructions for obtaining / releasing locks, tracing, &c.

- Dual-address space

- ▶ Primary & secondary spaces

- ▶ New instructions:

- PROGRAM CALL / PROGRAM RETURN

- INSERT / SET ADDRESS SPACE CONTROL

- MOVE TO PRIMARY / SECONDARY

6

In the late 1970s and early 1980s, additional features were added to the S/370 architecture.

26-bit real addressing allowed the machine to exploit 64 megabytes of real storage (after almost 14 years, the machines broke the 16 M-byte real boundary). The virtual space was still limited to 16 M-bytes, but since the operating system could support multiple spaces, 16 M-byte virtual was not considered to be a significant limitation (at the time).

Various special assist instructions were added for use by the MVS operating system. One of the performance bottlenecks in MVS was the tracing of key system functions ... special tracing instructions were added to improve the performance of these operations. Another bottleneck was the obtaining and releasing of global and local locks ... four specialized instructions were added to address this limitation. Two specialized instructions were added to assist the operation of supervisor-call (SVC) instructions, and adding functional-recovery routines. All of these instructions were privileged operations, available only to the control program.

Around 1981, IBM added the dual-address-space feature ... a means by which the program could, with special instructions, access two separate virtual address spaces with one instruction. A (relatively) primitive means of transferring control from a program running in one address space to another (and another ... &c) and safely returning was provided, as well as instructions to inspect and set address-space modes. Again, all of these instructions were privileged (or semi-privileged), thus control program assistance was necessary for their use.

## 370 Extended Architecture (1983)

- 31-bit virtual addressing

- ► Single address space providing up to 2 G-bytes

- ▶ Bimodal addressing (1 bit of address stolen to designate 24or 31-bit addresses)

- 31-bit real addressing (2 gigabytes max.)

- Most customers still had much less memory

- Entirely new I/O subsystem

- ▶ Up to 256 I/O channels

- New instructions for I/O, storage key manipulation, and program linkage

- Hardware tracing

7

With the growth of operating-system, database, and application usage, that 16 M-byte virtual constraint (that wasn't such a significant thing back late '70s) had suddenly become a critical limitation by the early 1980s. The 370 Extended Architecture (370/XA) feature provided significant relief ... providing 31-bit real and virtual addressing (that is, up to 2 G-bytes ... 128x the 16 M-byte limit) while retaining complete compatibility with 24-bit applications.

Why only 31-bit? That was part of the compatibility requirement ... the extra bit provided a means by which the program could switch back and forth between 24- and 31-bit addressing without any control-program intervention. As was the case when the original S/360 was introduced, 2 G-bytes of storage was not actually available at the time ... the largest real storage sold in the mid 1980s was in the range of a few hundred megabytes.

The entire I/O architecture – now called the channel subsystem – was redesigned, providing support for up to 256 I/O channels (again, more than any customer had for years to come), and around 14 new I/O instructions.

Other new instructions provided for better storage-key management (now on a 4 K-byte boundary instead of 2 K-byte), better cross-memory program linkage, and CPU-specific hardware tracing that significantly reduced the overhead of tracing.

#### Introduced access-register translation

- Provided the means by which a program could access multiple address spaces with minimum overhead

- ► Up to 2,048 2 G-byte address spaces (4 T-bytes)

- ► New *general* instructions for manipulation of ARs

- Introduced the home address space

- ► Location for principle task (process) control structures

- ▶ Where to go (i.e., who to blame) when task ABENDs

- Introduced the linkage stack

- ► Push-down stack for semi-authorized tasks

- ► New instructions for manipulation of linkage stack.

8

The size of a real or virtual space is often referred to as a vertical limit or a ceiling, and dealing with that limit involved a "horizontal" solution ... adding more virtual spaces. Recall that when the 16 M-byte boundary became an upper limit on addressability, one of the solutions was to introduce virtual memory, thus spreading this limit across multiple address spaces. 370/XA again raised the ceiling by providing a 2 G-byte limit, but in just a few short years, that was starting to seem tight. Additionally, the means of accessing data using the dual-address-space techniques was cumbersome and required constant intervention of the control program.

In 1989, IBM introduced the Enterprise Systems Architecture (ESA/370) which provided the access-register mode — a powerful means of dodging the 2 G-byte limit by again expanding horizontally, with up to 2,048 two G-byte space (a mind-boggling maximum of 4 terabytes!). With control program set-up, and very little intervention after that, application programs could easily manipulate storage in multiple address spaces without special semi-privileged instructions. And, the application could switch between any of the spaced it had been authorized to access.

ESA/370 also introduced the home address space, a special space designed to house principle task structures, such that when a program was multiple levels deep in calling programs in other address spaces – and an exception occurred – the control program would know to what task the fault should be attributed (that is, who gets ABENDed.

The program-call mechanism, introduced with the dual-address-space features back in 1981, were greatly expanded ... including a hardware-managed linkage stack. [When the original S/360 was designed, (most of) the chief architects were opposed to any sort of push-down stack (thinking it was a characteristic of a microcomputer). Curious that 25 years later, ESA/370 introduces a hardware-supported linkage stack that does much the same thing.]

As has been shown on many of the preceding slides, most of the new features added to the S/360 architecture have thus far been features that the control program exploits. Access registers starts to break this monopoly on improvements, providing the application with a powerful set of new instructions for data access. As will be seen on the next slide, significant architecture changes are added that are available to the application (nonprivileged) programs.

#### Numerous new facilities:

- ► Arithmetic instructions with 16-bit immediate operands

- ▶ Branch instructions with 16-bit relative-branch location

- ► Binary-floating-point instructions (IEEE standard)

- 95 new instructions and floating-point control register

- Compression facility

- Check-sum instruction

- ► Extended-translation instructions (Unicode<sup>TM</sup> conversion)

- **▶** Sorting-assist instructions

- ► String-manipulation instructions

- Enhancements to other facilities (PC, PR, &c).

9

During the 1990s, various facilities were added to the architecture to improve application programs:

A broad range of instructions having 16-bit immediate operands were added. The advantage was that a separate storage reference (other than the actual instruction itself) was not necessary to perform basic arithmetic and logical operations. For example, ADD IMMEDIATE allowed the addition of a signed 16-bit number to a register. This reduced storage access, thus minimizing unnecessary cache pollution by literal values.

Similarly, the relative-branching facility provided the means by which a program could perform forward or backward branches of up to 64K ... relative to the current instruction address in the PSW (rather than from a base register). This provided a significant increase in the range of branching (classic branching was limited to an unsigned 12-bit displacement). The relative-branching facility provided base-register constraint relief, and, with judicious use, made it possible to write some programs that did not require a base register at all.

The binary-floating-point facility provided 95 new instructions that conformed to the emerging IEEE floating-point standard (common in microprocessor platforms). This provided increased precision, with a smaller exponent "step" than in the classic S/360 floating-point number representation (now called hexadecimal floating point).

Numerous other new features were added, including a hardware-assisted compression facility, a check-sum facility in support of TCP/IP protocols, instructions for performing translation of Unicode character representations, manipulation of character strings (including Unicode strings) and assisting with DFSORT utilities. Other features were added to the linkage instructions (including the new PROGRAM RETURN instruction) for improved reliability in cross-memory applications.

- General registers grew to 64 bits

- Existing 32-bit instructions retained

- Used rightmost 32 bits of the 64-bit registers

- ► Large suite of 64-bit analogues added

- ▶ 163 new instructions (139 general, 11 control, 12 FP)

- Provides 64-bit virtual address space

- ▶ Up to 16 exabytes in a single space

- 18,446,744,073,709,551,616 bytes

- ▶ With ART, up to 2,048 spaces (2<sup>75</sup> bytes)

- 37,778,931,862,957,161,709,568 bytes

- ► Trimodal addressing: 24-, 31-, or 64-bit

- Provides 64-bit real

- ► Current models offer a few terabytes

We're starting to see a trend: Addressing hits a ceiling (16 M-byte), and then expands horizontally (multiple address spaces). Addressing is expanded, and again hits a ceiling (2 G-bytes), and then expands horizontally (access-register mode).

With z/Architecture, the number of addressing bits is more than doubled (to 64 from 31), and the number of addressable bytes increases by a factor of 8 billion – all while retaining compatibility with existing 24- and 31-bit applications. Sixty-four bit addressing provides support for both real and virtual spaces of sixteen exabytes! And with access-register translation, that's a maximum of thirty seven sextillion, seven hundred seventy eight quintillion, nine hundred thirty one quadrillion, eight hundred sixty two trillion, nine hundred fifty seven billion, one hundred sixty one million, seven hundred nine thousand, five hundred sixty eight bytes.

As with earlier extensions, the application program can switch between 24-, 31-, and 64-bit addressing without control program intervention. Unlike most of the preceding architecture enhancements that favored control-program features, z/Architecture provides 139 new general instructions ... most of which are 64-it analogs of existing 32-bit arithmetic and logical operations.

As seen with prior systems, current models of z/Architecture-capable machines offer much less than the maximum amount of memory addressable by the system.

Thus far, we have had a whirlwind review of the architecture that lead to System Z. The following slides will discuss enhancements that have been added to z/Architecture over the past 10 years.

## New Facilities in the Z800 & Z900 - Extended-Translation Facility 2:

- Performs operations on double-byte, ASCII, and decimal data.

- Provides support for manipulation of Unicode strings.

- Includes the following instructions:

| Name                         | Mne-<br>monic | Op-<br>code |

|------------------------------|---------------|-------------|

| COMPARE LOGICAL LONG UNICODE | CLCLU         | EB8F        |

| MOVE LONG UNICODE            | MVCLU         | EB8E        |

| PACK ASCII                   | PKA           | E9          |

| PACK UNICODE                 | PKU           | E1          |

| TEST DECIMAL                 | ТР            | EBC0        |

| TRANSLATE ONE TO ONE         | TROO          | B993        |

| TRANSLATE ONE TO TWO         | TROT          | B992        |

| TRANSLATE TWO TO ONE         | TRTO          | B991        |

| TRANSLATE TWO TO TWO         | TRTT          | B990        |

| UNPACK ASCII                 | UNPKA         | EA          |

| UNPACK UNICODE               | UNPKU         | E2          |

12

The extended-translation facility (now called **extended-translation facility 1**) was introduced in ESA/390 in 1999. It included the CONVERT UNICODE TO UTF-8, CONVERT UTF-8 TO UNICODE and TRANSLATE EXTENDED instructions.

To assist with the increasing handling of multinational character encodings – particularly those found in web pages – the **extended-translation-facility 2** provided the additional instructions shown in this slide.

Two instructions -- COMPARE LOGICAL LONG UNICODE and MOVE LONG UNICODE -- provide similar function to that of COMPARE LOGICAL LONG EXTENDED and MOVE LONG EXTENDED, respectively, except that the former pair provides 2 byte padding and requires the length to be a multiple of two.

Four instructions – PACK ASCII, PACK UNICODE, UNPACK ASCII, and UNPACK UNICODE – provide an efficient means of packing and unpacking data having character representations other than EBCDIC.

The four TRANSLATE N TO N instructions support translating between single-byte and double-byte character encodings.

- •Each instruction was designed to translate until a particular test character was encountered.

- •The two TRANSLATE TWO TO N instructions required that the translation table be on a 4K boundary.

The two characteristics enumerated above were not viewed as attractive features by some developers, and the ETF2-Enhancement Facility was later added to address these issues.

TEST DECIMAL was somewhat of an orphan, packaged into this facility. It tests for a valid packed-decimal digits and sign.

- Provides improved performance for hexadecimal floating-point numbers

- May be used in place of MULTIPLY followed by ADD (or SUBTRACT)

- Key to many improved mathematics functions

- Includes the following instructions:

| Name                  | Mne-<br>monic | Op-<br>code |

|-----------------------|---------------|-------------|

| MULTIPLY AND ADD      | MAD           | ED3E        |

| MULTIPLY AND ADD      | MADR          | B33E        |

| MULTIPLY AND ADD      | MAE           | ED2E        |

| MULTIPLY AND ADD      | MAER          | B32E        |

| MULTIPLY AND SUBTRACT | MSD           | ED3F        |

| MULTIPLY AND SUBTRACT | MSDR          | B33F        |

| MULTIPLY AND SUBTRACT | MSE           | ED2F        |

| MULTIPLY AND SUBTRACT | MSER          | B32F        |

MULTIPLY AND ADD and MULTIPLY AND SUBTRACT appeared in the architecture in earlier machines in the form of mathematical assists. With the advent of the binary floating-point (BFP) facility in ESA/390, MULTIPLY AND ADD / SUBTRACT were included as standard BFP instructions.

To provide equivalent function for the hexadecimal floating-point (HFP) formats, MULTIPLY AND ADD / SUBTRACT instructions were provided for HFP.

- Exploits previously-unused byte in RXE-format instruction:

- ► RXE-format instructions introduced with binaryfloating point in ESA/390

- ► RXE (and RSE) used extensively to implement z/Architecture opcodes (e.g., 64-bit instructions)

- ▶ Bits 32-39 of the instruction reserved in the new formats

The binary floating-point facility in ESA/390 introduced the RXE instruction format. Bits 8-31 of the RXE format provide the same register, base, index, and displacement fields as the RX format, however the opcode is 16 bits – split between the first and last bytes of the instruction. Bits 32-39 of the instruction are reserved.

With the advent of z/Architecture, the RS instruction format was extended in a similar manner to form the RSE format. The RSE and RXE instruction formats were used extensively in implementing the new 64-bit architecture.

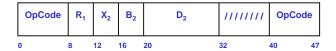

## Extends 12-bit unsigned displacement to 20-bit signed displacement:

► RSY:

| OpCode | R <sub>1</sub> | R <sub>3</sub> | B <sub>2</sub> | DL <sub>2</sub> | DH <sub>2</sub> | OpCode |

|--------|----------------|----------------|----------------|-----------------|-----------------|--------|

| 0      | 8              | 12             | 16             | 20              | 32              | 40 47  |

► RXY:

► SIY:

15

The long-displacement facility builds upon the RSE and RXE instruction formats introduced in z/Architecture. The new RSY and RXY instruction formats have all of the same fields as the RSE and RXE instructions, but with an additional field occupying the previously-reserved bits 32-39. A new SIY format, a long-displacement analog to the SI format, is also introduced.

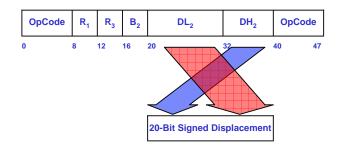

- Operand displacement-low field (DL) concatenated with displacement-high field (DH)

- ► Forms 20-bit signed displacement

- ▶ Bit 32 of the instruction is the sign bit

Prior to the long-displacement facility, the displacement field in an instruction was a 12-bit unsigned field, providing a displacement range from 0-4,095 bytes.

The new formats contain a 20-bit signed displacement, thus providing a positive or negative displacement of 512K.

Bits 32-39 of the instruction form the displacement high (DH) field that provides the most-significant bits of the displacement. Bit 32 is the sign bit.

The DH field, concatenated with the displacement low field (DL, that is, the classic 12-bit displacement in bits 20-31) form the 20-bit signed value.

- All RSE- and RXE-format instructions with primary opcode of E3 and EB changed to RSY and RXY format, respectively

- ► 69 z/Architecture instructions converted (64-bit operations)

- ► Floating-point ops not converted

- ▶ Decimal ops not converted

- ▶ No change to mnemonics

- 45 New RSY, RXY, and SIY-format instructions

- ► Most extend ESA/390-compatible 32-bit instructions

- ► Mnemonic suffixed with "Y" to indicate long displacement

- Example: New operation "LY" is analog to "L"

A significant number of the z/Architecture RSE and RXE instructions (that is, those that provided 64-bit support) were converted to long displacement (RSY and RXY format). Instruction-level compatibility for programs developed using 12-bit displacements is assured, since HLASM will generate zeros for the reserved fields.

Decimal and floating-point operations were not converted to long displacement.

New instructions were defined to provide long-displacement analogs for most of the 32-bit RS, RX, and SI instructions (that is, those ported to Z from ESA/390). The letter "Y" was appended to the mnemonic to indicate the long-displacement form. For example, the 32-bit LOAD includes both L and LY.

#### Advantages of long displacement

- ▶ Reduce the number of base registers required to address data

- Allows for non-zero-based structures

- Structures with prefix

- Certain stack models

- ► Opportunity for significant performance improvement

- Packing chained structured together

- Reduced address-generation interlocks (AGI)

- WARNING: Performance of long-displacement facility on Z800 & Z900 is suboptimal!

-18

There are numerous potential advantages to using the long-displacement facility:

- •The 12-bit displacement has been the bane of assembler programmers not long after the introduction of the S/360. Code that follows chains of pointers from a base structure to extension controls blocks can (conceivably) be redesigned to consolidate such linked control structures.

- •Certain control structures are not zero based. The long displacement provides an easy means of pointing a register at the nominal base on the structure, allowing the prefix portion to be referenced using a negative displacement.

However there are some potential drawbacks. The facility was first introduced with the z990 processors, where all of the facility is implemented in hardware. However, the facility was retrofit to the z800 and z900 systems, where it is implemented in Millicode. There are two separate facility indications for long displacement: the first indicates the presence of the facility, and the second indicates high performance.

- DAT-Enhancement Facility 1 (June 2003)

- High-Performance Long-Displacement Facility (June 2003)

- Message-Security Assist (June 2003)

- ► Five new instructions to perform CPU crypto operations

- **▶** Five query functions

- ► Two functions for message digest based on secure hash algorithm (SHA-1)

- ► Data-encryption-algorithm (DEA) functions

- More to follow in future machines

The z890 and z990 introduced a high-performance version of long-displacement. As discussed earlier, the version of long displacement provided on the z800 and z900 was done in Millicode.

The z890 and z990 also introduced the message-security assist, comprising five new multi-function instructions. Each instruction includes a query function that reports which additional functions are implemented for the instruction.

The basic assist includes a basic data-encryption-algorithm (DEA) function two secure-hash-algorithm functions (SHA-1). The assist is designed such that additional functions can be added in the future. A subsequent slide provides more details.

- Extended-translation facility 3 (May 2004)

- ► Performs operations on Unicode and Unicode-Transformation-Format (UTF) characters

- ► Provides right-to-left TRT

- ASN-and-LX-reuse facility (May 2004)

- ► Allows safe reuse of ASN

- **► Expands PC Number**

| Name                        | Mne-<br>monic | Op-<br>code |

|-----------------------------|---------------|-------------|

| CONVERT UTF-16 TO UTF-32    | CU24          | B9B1        |

| CONVERT UTF-32 TO UTF-16    | CU42          | B9B3        |

| CONVERT UTF-32 TO UTF-8     | CU41          | B9B2        |

| CONVERT UTF-8 TO UTF-32     | CU14          | B9B0        |

| SEARCH STRING UNICODE       | SRSTU         | B9BE        |

| TRANSLATE AND TEST REVERSED | TRTR          | D0          |

| Name                             | Mne-<br>monic | Op-<br>code |

|----------------------------------|---------------|-------------|

| EXTRACT PRIMARY ASN & INSTANCE   | EPAIR         | B99A        |

| EXTRACT SECONDARY ASN & INSTANCE | ESAIR         | B99B        |

| PROGRAM TRANSFER W / INSTANCE    | PTI           | B99E        |

| SET SECONDARY ASN W / INSTANCE   | SSAIR         | B99F        |

The extended-translation facility 3 provides additional instructions for processing for multiple-byte character representations such as Unicode.

In addition to the two Unicode conversion instructions added by the extended-translation facility 1, four additional instructions are added, providing a full complement of conversion options between 8-bit, 16-bit, and 32-bit Unicode representations. The two ETF-1 instructions CUTFU and CUUTF are given new mnemonics for consistency with the four new instructions.

SEARCH STRING UNICODE (SRSTU) provides an analog to the SEARCH STRING (SRST) instruction, except that SRSTU searches for a two-byte pattern.

TRANSLATE AND TEST REVERSE (TRTR) provides an analog to TRANSLATE AND TEST (TRT), except that TRTR operates in a right-to-left manner.

The ASN-and-LX-reuse facility (ALRF) extends the usability of address-space-number (ASN) and linkage-index (LX) translations by providing a separate instance number of (ASTEIN or LSTESN). Prior to ARLF, ASNs and LXs could not safely be reused due to the risk of a stale value being translated. The instance number (along with new checking and exceptions) assures that the ASN and/or LX can be reused.

The facility also expands the size of the PC number used by PROGRAM CALL to a 32-bit number (from a 20 bit number).

- Compare-and-swap-and-store facility

- Conditional-SSKE facility

- DAT-Enhancement Facility 2 (LPTEA)

- Decimal-floating-point facilities

- **ETF2-enhancement facility**

- **ETF3-enhancement facility**

- Extended-immediate facility

- Extract-CPU-time facility

- HFP-unnormalized extension

- Message-security-assist extension 1

- Move-with-optional-specifications facility

- Store-clock-fast facility

- Store-facility-list-extended facility

- TOD-clock-steering facility

The z9-109 series of processors introduced a substantial number of new facilities as enumerated on this slide. Each of these will be discussed in more detail on subsequent slides.

- Why decimal floating point?

- ► Given the normal supply of fingers, most people have a very particular affinity for base-10 arithmetic

- ► Imprecise binary representation of common decimal fractions (like 1/10)

- ► Accurate conversions between decimal and hex/binary is tricky

- -Rounding even trickier

- ▶ Emerging standard, expected to have impact on web applications

- What's needed?

- ► Intuitive arithmetic

- ► Exact representation of most decimal numbers

- ► Better handling of rounding

- ► Handle integers, fixed point, and floating point

Hexadecimal floating point has prevailed for over 43 years; the "new" binary floating point was introduced approximately 10 years ago. Why then, do we need yet another floating-point number representation?

Among other things, it comes down to the normal allotment of fingers – base 10 arithmetic is the form in which most people are trained. Other compelling factors include:

- •There are imprecise binary representations of very common decimal fractions such as 1/10.

- •Accurate conversion between binary formats (used by the CPU) and decimal formats (used in external representation) is tricky; rounding is even trickier.

- •Decimal floating point (DFP) is an emerging standard that is used in web applications today.

Decimal floating point provides for more intuitive arithmetic processing, more exact representation of most decimal numbers, better (well, more options for) rounding, and a means by which integers, fixed-point and floating-point can be represented.

But from the machine's perspective, it's a little trickier ...

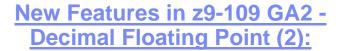

- DFP number representation:

- ► value = (-1)<sup>sign</sup> x coefficient x 10<sup>exponent</sup>

- Truly bizarre encoding:

- ► Sign (S)

- ► Combination field (CF)

- Two bits of biased exponent

- Leftmost digit (LMD) of coefficient

- Encoding of Infinity and Not-a-Number (NaN)

- . All 3 of the above mashed into 5 bits

- Biased exponent continuation field (BXCF)

- Remainder of biased exponent

- Includes controls for quiet or signaling NaNs

- Size depends on precision

- ► Encoded Trailing Significand (ETS)

- Remaining portion of the coefficient

- Size depends on precision

The number representation of a DFP number is as shown on this slide:

value = (-1)sign x coefficient x 10exponent

The encoding of a DFP value is rather unusual too, as shown on the slide.

- ■Perhaps the most recognizable field is a sign bit.

- ■The sign bit is followed by a five bit field, aptly named the combination field a highly encoded entity containing three separate components, including the leftmost digit (LMD) of the DFP number, two bits of the biased exponent field (more to follow), and an encoded indication of infinity or not-a-number (NaN).

- •Depending on the format of the DFP value, the biased exponent continuation (BXC) field contains either 6, 8, or 12 remaining bits of biased exponent. In more recent versions of the architecture, the BXC field is considered to be a part of the combination field.

- •Depending on the format of the DFP value, the encoded trailing significant (ETS) field contains either 20, 50, or 110 additional bits of the coefficient. This is cleverly encoded such that three decimal digits fit within 10 bits (with 24 possible decimal aliases).

The three formats of a DFP floating-point number are shown on this slide.

Note that both the combination field and the encoded-trailing-significand field vary in size from one format to another.

## New Features in z9-109 GA2 - Decimal Floating Point (3):

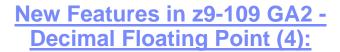

### ■ Summary of DFP Formats

| Property                                       | Short                                    | Long                                       | Extended                                    |

|------------------------------------------------|------------------------------------------|--------------------------------------------|---------------------------------------------|

| Format length (bits)                           | 32                                       | 64                                         | 128                                         |

| Combination length (bits)                      | 11                                       | 13                                         | 17                                          |

| Encoded trailing significand length (bits)     | 20                                       | 50                                         | 110                                         |

| Precision (digits), p                          | 7                                        | 16                                         | 34                                          |

| Maximum left-units-view (LUV) exponent (Emax)  | 96                                       | 384                                        | 6144                                        |

| Minimum left-units-view (LUV) exponent (Emin)  | -95                                      | -383                                       | -6143                                       |

| Left-units-view (LUV) bias                     | 95                                       | 383                                        | 6143                                        |

| Maximum right-units-view (RUV) exponent (Qmax) | 90                                       | 369                                        | 6111                                        |

| Minimum right-units-view (RUV) exponent (Qmin) | -101                                     | -398                                       | -6176                                       |

| Right-units-view (RUV) bias                    | 101                                      | 398                                        | 6176                                        |

| Maximum biased exponent                        | 191                                      | 767                                        | 12,287                                      |

| Largest (in magnitude) normal number, Nmax     | (10 <sup>7</sup> – 1) x 10 <sup>90</sup> | (10 <sup>16</sup> – 1) x 10 <sup>369</sup> | (10 <sup>34</sup> – 1) x 10 <sup>6111</sup> |

| Smallest (in magnitude) normal number, Nmin    | 1 x 10 <sup>-95</sup>                    | 1 x 10 <sup>-383</sup>                     | 1 x 10 <sup>-6143</sup>                     |

| Smallest (in magnitude) subnormal number, Dmin | 1 x 10 <sup>-101</sup>                   | 1 x 10 <sup>-398</sup>                     | 1 x 10 <sup>-6176</sup>                     |

25

This slide enumerates the various characteristics of the three DFP formats.

#### DFP Facility:

- ▶ 54 problem-state instructions for:

- Adding

- Comparing to / from fixed, signed BCD, unsigned BCD

- Converting

- Dividing

- Extracting exponent, significance

- Loading and testing, lengthening, rounding

- Multiplying

- Quantizing

- Shifting

- Subtracting

- Testing data classes

- Testing data groups

26

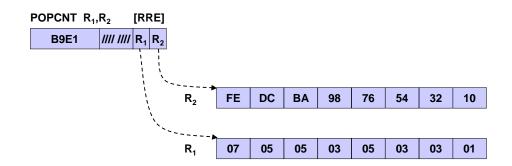

The basic DFP facility includes 54 problem-state instructions that perform the operations enumerated on this slide. These instructions were added to the *z/Architecture Principles of Operation* (SA22-7832-05) in Chapter 20. Note that numerous other changes were made to Chapters 9, 18, and 19 in support of DFP.

The majority of DFP instructions are of one of the register-to-register formats (RRE, RRF or RRR), operating on values that have been preloaded into floating-point registers. Exceptions are the SHIFT instructions (RXF format) and the TEST DATA CLASS / GROUP instructions (RXE format).

#### Control via:

- ► Additional-floating-point (AFP) control (CR0.45)

- ► Floating-point-control (FPC) register

- New DFP rounding-mode control with 8 options.

- **z**9-109 implementation done in Firmware (with hardware assists)

- ▶ Compared to web-based emulations written in C (or Java), performance is superior.

- ► All-hardware implementation in System z10 and above

27

As with the binary-floating-point facility, control of DFP is by means of the additional-floating-point (AFP) control (bit 45 of control register 0) and the floating-point-control (FPC) register.

A new DFP rounding mode has been added to the FPC register (bits 25-27), with 8 rounding options:

000 - round to nearest with ties to even

001 - round toward 0

010 - round toward positive infinity

011 - round toward negative infinity

100 - round to nearest with ties away from zero

101 - round to nearest with ties toward zero

110 - round away from 0

111 - round to prepare for shorter precision

The initial (z9-109) implementation of DFP is done in processor firmware using specialized hardware assists. Although this is not as fast as an all-hardware implementation, it is significantly faster than web-based emulations written in Java or C++. Future implementations are planned to be all hardware.

- DFP Rounding Facility:

- ► SET DFP ROUNDING MODE instruction (and associated rounding modes in FPC register).

- Floating-Point-Support-Sign-Handling Facility:

- COPY SIGN

- **▶ LOAD COMPLEMENT**

- **► LOAD NEGATIVE**

- **▶ LOAD POSITIVE**

- FPR-GR-Transfer Facility:

- **▶ LOAD FPR FROM GR**

- ► LOAD GR FROM FPR

- IEEE-Exception-Simulation Facility:

- **▶ SET FPC AND SIGNAL**

- **▶ LOAD FPC AND SIGNAL**

- PERFORM FLOATING POINT OPERATION (PFPO)

- ► Conversion to/from HFP / BFP / DFP

- Numerous rounding-mode options

Several floating-point-support facilities were introduced coincident with the DFP facility, as shown on this slide. These are all documented in Chapter 9 of the *z/Architecture Principles of Operation* (SA22-7832-05).

As mentioned in the notes for slide 23, the majority of DFP instructions operate on floating-point registers. The standard floating-point-support LOAD instructions – LD, LDY, LE, and LEY – can be used to load the FP registers from storage; LDR, LER, and LXR can be used to copy from one FPR to another. The FPR-GPR transfer facility provides the means by which data can be interchanged between FP registers and general registers.

The IEEE-exception-simulation facility provides a means of testing IEEE exception conditions by software simulation – without actually forcing the arithmetic condition to occur.

#### Adds numerous 32-bit immediate-operand instructions

- ► ADD IMMEDIATE (AFI, AGFI)

- ► ADD LOGICAL IMMEDIATE (ALFI, ALGFI)

- ► AND IMMEDIATE (NIHF, NILF)

- **► COMPARE IMMEDIATE (CFI, CGFI)**

- ► COMPARE LOGICAL IMMEDIATE (CLFI, CLGFI)

- **► EXCLUSIVE OR IMMEDIATE (XIHF, XILF)**

- ► INSERT IMMEDIATE (IIHF, IILF)

- ► LOAD IMMEDIATE (LGFI)

- ► LOAD LOGICAL IMMEDIATE (LLIHF, LLILF)

- ► OR IMMEDIATE (OIHF, OILF)

- **► SUBTRACT LOGICAL IMMEDIATE (SLFI, SLGFI)**

- Minimizes need for constants & literal pools

29

The immediate-and-relative-instruction facility (circa 1996) introduced a number of instructions with 16-bit immediate operands, for example LOAD HALFWORD IMMEDIATE. These ESA/390 instructions became part of the base z/Architecture.

The **extended-immediate facility** adds several instructions with 32-bit immediate fields, performing the basic arithmetic, logical, and comparison functions enumerated on this slide. One advantage of having immediate operands is that once the instruction is fetched, there is no separate fetch required for the immediate operand.

Note, the base z/Architecture provided 16-bit versions of AND IMMEDIATE and OR IMMEDIATE, but not EXCLUSIVE OR IMMEDIATE. The extended-immediate facility provides 32-bit versions of all of these instructions (but still no 16-bit exclusive-OR operation).

- Adds numerous miscellaneous instructions

- ► FIND LEFTMOST ONE (FLOGR)

- ► LOAD AND TEST (LT, LTG)

- Adds RXE-format to existing RR- and RRE-formats.

- ► LOAD BYTE (LBR, LGBR)

- Adds RRE format to existing LB and LGB

- ► LOAD HALFWORD (LHR, LGHR)

- Adds RRE format to existing LH and LGH

- ► LOAD LOGICAL CHARACTER (LLC, LLCR, LLGCR)

- Adds 32-bit RXY-format, and 32- and 64-bit RRE-formats

- ► LOAD LOGICAL HALFWORD (LLH, LLHR, LLGHR)

- Adds 32-bit RXY-format, and 32- and 64-bit RRE-formats

- Advantages:

- **▶** Fewer storage references

- ► Smaller code image

The extended-immediate facility also includes several other non-immediate-related instructions, as enumerated on this slide.

FIND LEFTMOST ONE returns the bit position of the leftmost one in one register, and the original operand with the leftmost one turned off in another register. It is particularly useful in manipulating bit maps.

LOAD AND TEST (LT, LTG) provide for the loading from storage and testing of a value. It is similar to the combination of L/LT (or LG/LTG), but in a single instruction. Note, ICM is not truly equivalent, as it provides neither an index register nor support of 64-bit values.

The extended-immediate facility provides the potential of improving code performance by reducing storage references (having an immediate operand fetched along with the instruction). The additional instructions listed on this slide provide additional utility in a single instruction, combining what previously might take multiple instructions to provide equivalent function.

- Original STORE CPU TIMER (STPT) is a privileged instruction

- ▶ z/OS TIMEUSED service routine:

- -Extracts CPU timer for problem-state programs

- -Takes hundreds of CPU cycles (PC, lock, disable, observe, enable, unlock, PR)

- -Significantly skews measurements

- **EXTRACT CPU TIME (ECTG) instruction:**

- ▶ Problem-state instruction

- ► Can provide most data provided by TIMEUSED

- ► Substantially less overhead

- ► May facilitate better measurement of module flow, instruction sequences, micro-accounting, &c.

- ► Requires access to SCP-maintained fields:

- -Task-time used

- -CPU timer at last dispatch

- -Scaling factor for secondary CPUs.

Accurate observations of CPU utilization require the inspection of the CPU timer. However, the STORE PROCESSOR TIMER (STPT) instruction is privileged and is not available to the application program. The primary reason for this restriction is that, without serialized observation of other data maintained by the operating system, the results of STPT are meaningless. This is because, between one observation and the next, the program may be interrupted, and the operating system may alter the contents of the CPU timer without the program's knowledge.

z/OS provides the TIMEUSED service for extracting a task's accumulated CPU time, however older versions of the service routine are invoked by means of PROGRAM CALL and consumes hundreds of cycles. For a program that needs to measure the CPU time of a small code fragment, the overhead of the TIMEUSED service may obscure what is actually being measured.

The EXTRACT CPU TIME (ECTG) instruction provides a means by which a problem-state application program can inspect the CPU timer and other SCP-maintained timer-related fields as a single unit of operation. This provides a task with a means of efficiently determining total elapsed CPU time from which other timing-related data can be derived.

The z/OS TIMEUSED service has been adapted to use the ECTG instruction; TIMEUSED may now be entered via a branch rather than PROGRAM CALL.

- Adds unnormalized versions of MULTIPLY and MULTIPLY AND ADD to hexadecimal floating point

- Useful in multi-precision and crypto applications

- All are RRF-format ops.

| Name                          | Mne-<br>monic | Op-<br>code |

|-------------------------------|---------------|-------------|

| MULTIPLY UNNORMALIZED         | MYR           | B33B        |

| MULTIPLY UNNORMALIZED         | MYHR          | B33D        |

| MULTIPLY UNNORMALIZED         | MRLR          | B339        |

| MULTIPLY UNNORMALIZED         | MY            | ED3B        |

| MULTIPLY UNNORMALIZED         | MYH           | ED3D        |

| MULTIPLY UNNORMALIZED         | MYL           | ED39        |

| MULTIPLY AND ADD UNNORMALIZED | MAXWR         | B33A        |

| MULTIPLY AND ADD UNNORMALIZED | MAWR          | B33C        |

| MULTIPLY AND ADD UNNORMALIZED | MAYWR         | B338        |

| MULTIPLY AND ADD UNNORMALIZED | MAXW          | ED3A        |

| MULTIPLY AND ADD UNNORMALIZED | MAW           | ED3C        |

| MULTIPLY AND ADD UNNORMALIZED | MAYW          | ED38        |

Slide 5 discussed the addition of hexadecimal-floating-point (HFP) multiply-and-add and multiply-and-subtract instructions. Similar functions were already provided for binary floating point.

The HFP unnormalized extension facility adds unnormalized versions of HFP MULTIPLY and MULTIPLY AND ADD instructions.

- Adds two 256-bit secure-hash-algorithm (SHA) functions:

- **► COMPUTE INTERMEDIATE MESSAGE DIGEST**

- **▶ COMPUTE FINAL MESSAGE DIGEST**

- Adds two 128-bit advanced-encryption-standard (AES)

#### functions:

- **► CIPHER MESSAGE WITH CHAINING**

- ► CIPHER MESSAGE (sans chaining)

- Adds 64-bit pseudo-random-number-generation facility

- ► CIPHER MESSAGE WITH CHAINING

- All are extensions to message-security assist added in z990 GA1.

33

As noted on slide 13, there may be future extensions to the Message-Security Assist. The MSA-Extension-Assist Extension 1 is the first of these.

MSA-X1 includes the following enhancements:

- •For the CIPHER MESSAGE and CIPHER MESSAGE WITH CHAINING instructions, two 128-bit advanced-encryption-standard (AES) operations are added.

- •For CIPHER MESSAGE WITH CHAINING, a 64-bit pseudo-random-number-generation facility is added.

- •For COMPUTE INTERMEDIATE MESSAGE DIGEST and COMPUTE FINAL MESSAGE DIGEST, two 256-bit secure-hash-algorithm functions are added.

- MVCOS provides über MOVE CHARACTER

- ► True length specified in a register (no need for EXECUTE)

- ► Moves up to 4K in one execution

- ▶ Moves from any address-space control (ASC) to any other

- ► Moves from any key to any other

- ► Key and ASC for source and destination may be explicitly programspecified or use current-PSW values

- ▶ May be faster than MOVE LONG for 4K-byte moves, but ...

- ▶ Will likely be slower than executed MVC for < 256-byte move.

- Equivalent to MVCP, MVCS, MVCDK, MVCSK, MVCK

- ► Except the above are limited to 256 bytes; MVCOS is not.

- ► Available to problem-state code (subject to PSW key mask)

MOVE WITH OPTIONAL SPECIFICATIONS provides functions similar to that of MOVE TO PRIMARY, MOVE TO SECONDARY, MOVE WITH DESTINATION KEY, MOVE WITH KEY, and MOVE WITH SOURCE KEY – and much more.

The source and target operands are both base/displacement storage operands (sorry, short displacement only). General register 1 contains a true length value; up to 4,096 bytes may be moved for each execution.

General register 0 contains operand-access controls (OAC) for both the source and target operands. For each operand, the OAC contains specifications as to the storage key and address-space control (ASC) to be used for accessing the operand. The storage key may either be that of the current PSW or that specified in the OAC. Similarly, the address space control may be either that of the current PSW or that specified in the OAC. When GR0 contains zero, the source and target key/ASC values come from the PSW.

When executed in the problem state, the key specifications for both operands must be valid in the PSW key mask (CR3.32-47).

The instruction does not perform operand-overlap checking (unlike MVCL). However, because MVCOS performs several other authorization checks, its performance may be less than MVCL.

The instruction can specify any address-space control, however specification of AR-mode ASC is not particularly useful: If you already have access-register capability, then any other move instruction (e.g., MVC) can be used.

- STORE CLOCK FAST allows storing of full-resolution 64bit clock

- ► Same clock value may be seen by the same or other CPUs multiple times.

- ▶ Should be used only by applications that can tolerate it

- -Duplicate time stamps means exact sequence cannot be determined in an MP environment!

- ► STCKF (B27C hex) can replace STCK (B205 hex)

- TRACE instruction can also use STCKF format

- ► Subject to control register 0, bit 32.

- Facility is not required if program switches to STORE CLOCK EXTENDED and TRACE (TRACG)

STORE CLOCK FAST (STCKF) allows the storing of a full-resolution 64-bit clock value. The rules for monotonic advancement are relaxed such that the same time stamp may be stored multiple times by one or more CPUs. However, the clock will **never** appear to run backwards.

STCKF should only be used by applications that can tolerate observing the same clock value twice. The potential for duplicate TOD values being stored may mean that the program cannot determine which event occurred first (unless some other form of serialization is used).

A portion of the TOD clock is also stored in trace records created by the TRACE (32-bit) instruction. Subject to bit 32 of control register 0, TRACE can be directed to store a result as if STCKF had been used (when CR0.32 is zero, it's business as usual, thus assuring compatibility with earlier programs).

When STORE CLOCK EXTENDED is used (or the 64-bit TRACG), the store-clock-fast facility is unnecessary.

#### Original z/Architecture STORE FACILITY LIST (STFL):

- ► Stores a list of facility bits at real location 200 (C8 hex)

- ► Privileged operation (supervisor state)

- ► Inaccessible unless SCP maps real 0 to virtual 0

- Z/OS does

- Linux doesn't

- ► Limited to 32 facilities (one word potentially extendable)

#### STORE FACILITY LIST EXTENDED (STFLE)

- ► General instruction (problem state)

- ► Stores the results in a program-specified location and length

- ► Up to 16,384 facilities may be indicated

- ► Maps the first 32 facilities the same as STFL

36

The original STORE FACILITY LIST (STFL) instruction had several limitations:

- Only 32 facility bits are supported

- •The results are placed in real storage location 200 (C8 hex). Although z/OS maps real page 0 in a V=R manner, Linux does not.

- ■STFL is a privileged instruction.

Thus, for environments such as Linux, a costly system call is required to determine what hardware facilities are available.

STORE FACILITY LIST EXTENDED (STFLE) is intended to address all of these concerns, as follows:

- •STFLE is a general instruction, thus any application can execute it.

- •The results are stored in a program-specified location.

- •Up to 16K of facility indications may be indicated (256 doublewords; 1 bit per facility indication).

- •The first 32 facility indications are identical to that provided by STFL.

z/OS continues to store facility indications at location 200, but now it uses STFLE instead of STFL. Thus facilities 32 and above may be indicated in real locations 204 and up, such that the z/OS application does not need STFLE at all.

37

The following slides will discuss the following facilities that were introduced on the z800 and z900 processors:

- ■Extended-translation facility 2

- ■HFP Multiply-and-Add / Subtract

- ■Long Displacement

### Instruction categories:

- ► Cache cognizance

- ► Compare [logical] [immediate] and branch [relative]

- ► Compare [logical] [immediate] and trap

- ► Immediate second-operand field

- ► Relative-long second operand

- ► Rotate then {AND | OR | XOR | Insert} selected bits

- **►** Miscellany

- Primary motivation: PERFORMANCE!

The general-instructions-extension facility (GIEF) was primarily developed in response to requirements from IBM's compiler-development organization in Toronto. As noted on this slide, performance was the driving factor in implementing (most of) these instructions.

For presentation purposes, the 72 instructions of the GIEF are divided into several categories, based on the instructions' characteristics. In some cases, an instruction's category characteristics overlap – for example, PREFETCH DATA RELATIVE LONG, which is described in the cache-cognizance category – also has the relative-long-second-operand characteristic. When such ambiguity exists, the instruction is described under the category that represents a best fit.

**Note:** In subsequent slides, the notation "SSS...SSS" means that the operand is sign-extended to the left to match the size of the other operand. Similarly, notation "000...000" means that the operand is zero-extended to the left to match the size of the other operand.

## **General-Instructions Extension Facility: Cache Cognizance Instructions**

| Instruction                 | Mne-  | Ор-  | First Operand |      | Second Operand |      |

|-----------------------------|-------|------|---------------|------|----------------|------|

|                             | monic | Code | Location      | Size | Location       | Size |

| EXTRACT CACHE ATTRIBUTE     | ECAG  | EB4C | Register      | 64   | S(20)          | N/A  |

| PREFETCH DATA               | PFD   | E336 | Mask          | 16   | S(20)          | MD   |

| PREFETCH DATA RELATIVE LONG | PFDRL | C62  | Mask          | 16   | RL             | MD   |

#### **Explanation:**

N/A Not applicable

MD Model Dependent

RL Relative-long operand; 32-bit immediate value, multiplied by two and added to the current

instruction address, provides the storage location of the operand

S(20) Storage operand addressed using base, index, and 20-bit signed displacement.

3<u>Mdex</u>

Three instructions fall into the cache-cognizance category:

EXTRACT CACHE ATTRIBUTE provides a means by which various characteristics of a CPU's cache(s) may be determined.

PREFETCH DATA and PREFETCH DATA RELATIVE LONG provide the means by which a storage operand may be fetched into – or released from – a cache line.

## General-Instructions Extension Facility: Compare [Logical] [Immediate] and Branch [Relative]

| Instruction                                   | Mne-  | Op-  | First Operand | I    | Second Opera | nd   | Branch   |

|-----------------------------------------------|-------|------|---------------|------|--------------|------|----------|

|                                               | monic | Code | Location      | Size | Location     | Size | Location |

| COMPARE AND BRANCH                            | CRB   | ECF6 | Register      | 32   | Register     | 32   | S(12)    |

| COMPARE AND BRANCH                            | CGRB  | ECE4 | Register      | 64   | Register     | 64   | S(12)    |

| COMPARE AND BRANCH RELATIVE                   | CRJ   | EC76 | Register      | 32   | Register     | 32   | Relative |

| COMPARE AND BRANCH RELATIVE                   | CGRJ  | EC64 | Register      | 64   | Register     | 64   | Relative |

| COMPARE IMMEDIATE AND BRANCH                  | CIB   | ECFE | Register      | 32   | Immediate    | 8    | S(12)    |

| COMPARE IMMEDIATE AND BRANCH                  | CGIB  | ECFC | Register      | 64   | Immediate    | 8    | S(12)    |

| COMPARE IMMEDIATE AND BRANCH RELATIVE         | CIJ   | EC7E | Register      | 32   | Immediate    | 8    | Relative |

| COMPARE IMMEDIATE AND BRANCH RELATIVE         | CGIJ  | EC7C | Register      | 64   | Immediate    | 8    | Relative |

| COMPARE LOGICAL AND BRANCH                    | CLRB  | ECF7 | Register      | 32   | Register     | 32   | S(12)    |

| COMPARE LOGICAL AND BRANCH                    | CLGRB | ECE5 | Register      | 64   | Register     | 64   | S(12)    |

| COMPARE LOGICAL AND BRANCH RELATIVE           | CLRJ  | EC77 | Register      | 32   | Register     | 32   | Relative |

| COMPARE LOGICAL AND BRANCH RELATIVE           | CLGRJ | EC65 | Register      | 64   | Register     | 64   | Relative |

| COMPARE LOGICAL IMMEDIATE AND BRANCH          | CLIB  | ECFF | Register      | 32   | Immediate    | 8    | S(12)    |

| COMPARE LOGICAL IMMEDIATE AND BRANCH          | CLGIB | ECFD | Register      | 64   | Immediate    | 8    | S(12)    |

| COMPARE LOGICAL IMMEDIATE AND BRANCH RELATIVE | CLIJ  | EC7F | Register      | 32   | Immediate    | 8    | Relative |

| COMPARE LOGICAL IMMEDIATE AND BRANCH RELATIVE | CLGIJ | EC7D | Register      | 64   | Immediate    | 8    | Relative |

S(12) Storage operand addressed using base, index, and 12-bit unsigned displacement.

4<u>Qdex</u>

The COMPARE AND BRANCH instructions combine a compare operation and, if the specified condition is met, a branch operation, in a single instruction. When the specified condition is not met, execution continues with the next sequential instruction. Many forms of the instruction are provided based on these characteristics:

- · Numeric attribute: signed versus unsigned

- · Operand size: 32-bit versus 64-bit

- · Second-operand location: register versus immediate field

- Branch designation: base and 12-bit displacement versus 16-bit signed relative

As can be seen in the subsequent slides, the instructions have a rich set of operands. For the instruction formats with the comparand (second operand) in an immediate field, there is only room for an 8-bit value.

For each of the COMPARE AND BRANCH (and COMPARE AND TRAP) instructions, the High Level Assembler implements extensions to the mnemonics in lieu of the  $M_3$  field. The extensions include:

| E  | equal     | $M_3 = 1000 \text{ binary}$  |

|----|-----------|------------------------------|

| Н  | high      | $M_3 = 0010 \text{ binary}$  |

| L  | low       | M <sub>3</sub> = 0100 binary |

| NE | not equal | $M_3 = 0110 \text{ binary}$  |

| NH | not high  | M <sub>3</sub> = 1100 binary |

| NL | not low   | $M_3 = 1010 \text{ binary}$  |

When the mnemonic extension is coded, the  ${\rm M}_{\rm 3}$  field must be omitted.

## **General-Instructions Extension Facility: Compare [Logical] [Immediate] and Trap**

| Instruction                        | monic Code | First Operand |          | Second Operand |           |      |

|------------------------------------|------------|---------------|----------|----------------|-----------|------|

|                                    | monic      | Code          | Location | Size           | Location  | Size |

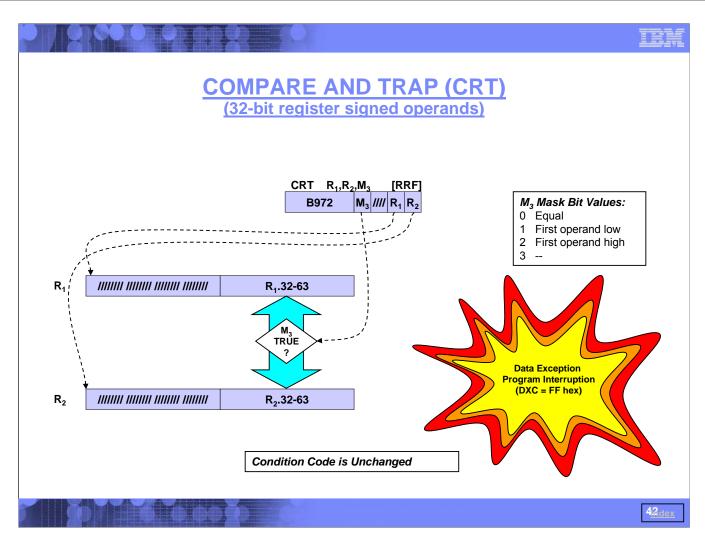

| COMPARE AND TRAP                   | CRT        | B972          | Register | 32             | Register  | 32   |

| COMPARE AND TRAP                   | CGRT       | B960          | Register | 64             | Register  | 64   |

| COMPARE IMMEDIATE AND TRAP         | CIT        | EC72          | Register | 32             | Immediate | 16   |

| COMPARE IMMEDIATE AND TRAP         | CGIT       | EC70          | Register | 64             | Immediate | 16   |

| COMPARE LOGICAL AND TRAP           | CLRT       | B973          | Register | 32             | Register  | 32   |

| COMPARE LOGICAL AND TRAP           | CLGRT      | B961          | Register | 64             | Register  | 64   |

| COMPARE LOGICAL IMMEDIATE AND TRAP | CLFIT      | EC73          | Register | 32             | Immediate | 16   |

| COMPARE LOGICAL IMMEDIATE AND TRAP | CLGIT      | EC71          | Register | 64             | Immediate | 16   |

The COMPARE AND TRAP instructions combine a compare operation and, if the specified condition is met, a program interruption, in a single instruction. When the specified condition is met, a data-exception program interruption is generated with a data-exception code (DXC) of FF hex. When the specified condition is not met, execution continues with the next sequential instruction. Many forms of the instruction are provided based on these characteristics:

· Numeric attribute: signed versus unsigned

· Operand size: 32-bit versus 64-bit

· Second-operand location: register versus immediate field

Because there is no branch location required (as in COMPARE AND BRANCH), the instruction formats with an immediate-field comparand provide a 16-bit value.

For each of the COMPARE AND TRAP instructions, the High Level Assembler implements extensions to the mnemonics in lieu of the M<sub>3</sub> field, as described in the notes for COMPARE AND BRANCH.

COMPARE AND TRAP is useful in a coding environment where a comparison is required (for example, checking for a null pointer), but the program is not immediately concerned with the recovery from such a comparison. Rather, if the comparison results in a true condition, the recovery is escalated to whatever recovery routine (if any) is provided.

COMPARE AND TRP (CRT) compares the 32-bit signed binary integer in bits 32-63 of the first-operand register with a 32-bit signed binary integer in the corresponding bits in the second-operand register.

If the conditions specified by the mask field (the third operand) are true, then a data exception program-interruption condition is recognized. The data-exception code (DXC) contains FF hex.

If the conditions specified by the mask field are not true, then execution continues with the next sequential instruction.

## **General-Instructions Extension Facility: Immediate Second-Operand Instructions**

| Instruction                       | Mne- Op- |      | First Operand |      |      | Second Operand |      |      |

|-----------------------------------|----------|------|---------------|------|------|----------------|------|------|

|                                   | monic    | Code | Location      | Size | Sign | Location       | Size | Sign |

| ADD IMMEDIATE                     | ASI      | EB6A | S(20)         | 32   | s    | Immediate      | 8    | s    |

| ADD IMMEDIATE                     | AGSI     | EB7A | S(20)         | 64   | s    | Immediate      | 8    | s    |

| ADD LOGICAL WITH SIGNED IMMEDIATE | ALSI     | EB6E | S(20)         | 32   | U    | Immediate      | 8    | s    |

| ADD LOGICAL WITH SIGNED IMMEDIATE | ALGSI    | EB7E | S(20)         | 64   | U    | Immediate      | 8    | s    |

| COMPARE HALFWORD IMMEDIATE        | CHHSI    | E554 | S(12)         | 16   | s    | Immediate      | 16   | s    |

| COMPARE HALFWORD IMMEDIATE        | CHSI     | E55C | S(12)         | 32   | s    | Immediate      | 16   | s    |

| COMPARE HALFWORD IMMEDIATE        | CGHSI    | E558 | S(12)         | 64   | s    | Immediate      | 16   | s    |

| COMPARE LOGICAL IMMEDIATE         | CLHHSI   | E555 | S(12)         | 16   | U    | Immediate      | 16   | U    |

| COMPARE LOGICAL IMMEDIATE         | CLFHSI   | E55D | S(12)         | 32   | U    | Immediate      | 16   | U    |

| COMPARE LOGICAL IMMEDIATE         | CLGHSI   | E556 | S(12)         | 64   | U    | Immediate      | 16   | U    |

| MOVE [IMMEDIATE]                  | MVHHI    | E544 | S(12)         | 16   | s    | Immediate      | 16   | s    |

| MOVE [IMMEDIATE]                  | MVHI     | E54C | S(12)         | 32   | s    | Immediate      | 16   | s    |

| MOVE [IMMEDIATE]                  | MVGHI    | E548 | S(12)         | 64   | s    | Immediate      | 16   | s    |

| MULTIPLY SINGLE IMMEDIATE         | MSFI     | C21  | Register      | 32   | s    | Immediate      | 32   | s    |

| MULTIPLY SINGLE IMMEDIATE         | MSGFI    | C20  | Register      | 64   | s    | Immediate      | 32   | s    |

A large variety of instructions are added with the second operand specified as an immediate field.

Of particular note is that for ADD IMMEDIATE, ADD LOGICAL WITH SIGNED IMMEDIATE, COMPARE HALFWORD IMMEDIATE, COMPARE LOGICAL IMMEDIATE, and MOVE (the first 15 instructions listed), the first operand is a <u>storage location</u> designated by a base register and 12-bit unsigned displacement field. More notes on ADD LOGICAL WITH SIGNED IMMEDIATE appear with that slide.

There are previously-existing forms of MULTIPLY with an immediate operand. The two forms shown here provide the immediate multiplier to the MULTIPLY SINGLE instructions.

## **General-Instructions Extension Facility: Relative-Long Second Operands (1 of 2)**

| Instruction                    | Mne-   | ' L  | First Operand | ı    | Second Operand |                   |

|--------------------------------|--------|------|---------------|------|----------------|-------------------|

|                                | monic  | Code | Location      | Size | Location       | Size <sup>‡</sup> |

| COMPARE RELATIVE LONG          | CRL    | C6D  | Register      | 32   | RL             | 32                |

| COMPARE RELATIVE LONG          | CGFRL  | C6C  | Register      | 64   | RL             | 32                |

| COMPARE RELATIVE LONG          | CGRL   | C68  | Register      | 64   | RL             | 64                |

| COMPARE HALFWORD RELATIVE LONG | CHRL   | C65  | Register      | 32   | RL             | 16                |

| COMPARE HALFWORD RELATIVE LONG | CGHRL  | C64  | Register      | 64   | RL             | 16                |

| COMPARE LOGICAL RELATIVE LONG  | CLRL   | C6F  | Register      | 32   | RL             | 32                |

| COMPARE LOGICAL RELATIVE LONG  | CLGFRL | C6E  | Register      | 64   | RL             | 32                |

| COMPARE LOGICAL RELATIVE LONG  | CLGRL  | C6A  | Register      | 64   | RL             | 64                |

| COMPARE LOGICAL RELATIVE LONG  | CLHRL  | C67  | Register      | 32   | RL             | 16                |

| COMPARE LOGICAL RELATIVE LONG  | CLGHRL | C66  | Register      | 64   | RL             | 16                |

#### **Explanation:**

Operand must be aligned on an integral boundary; otherwise, a specification exception is

recognized!

RL Relative-long operand; 32-bit immediate value, multiplied by two and added to the current

instruction address, provides the storage location of the operand

4<u>Mdex</u>

GIEF introduces variations of existing compare, load, and store instructions in which the second operand is specified as a relative-long storage location. As stated with PFDRL, relative-long storage specifications are new with the System z10 EC; they are similar to the relative and relative-long branch-address specifications, already present in the architecture.

For a relative-long storage specification, the immediate field is a signed value that designates the number of halfwords added to the current instruction address to form the address of the storage location (subject to the current addressing mode). More succinctly:

storage\_location = I<sub>2</sub> x 2 + current\_instruction\_address

Because the  $I_2$  field is signed, the storage location may precede the current instruction address if  $I_2$  is negative. The storage location is always in the same address space from which instructions are being fetched.

See alignment notes accompanying the following slide.

## **General-Instructions Extension Facility: Relative-Long Second Operands (2 of 2)**

| Instruction                         | Mne-   | Ор-  | First Ope | rand Second C |          | perand            |  |

|-------------------------------------|--------|------|-----------|---------------|----------|-------------------|--|

|                                     | monic  | Code | Location  | Size          | Location | Size <sup>‡</sup> |  |

| LOAD RELATIVE LONG                  | LRL    | C4D  | Register  | 32            | RL       | 32                |  |

| LOAD RELATIVE LONG                  | LGFRL  | C4C  | Register  | 64            | RL       | 32                |  |

| LOAD RELATIVE LONG                  | LGRL   | C48  | Register  | 64            | RL       | 64                |  |

| LOAD HALFWORD RELATIVE LONG         | LHRL   | C45  | Register  | 32            | RL       | 16                |  |

| LOAD HALFWORD RELATIVE LONG         | LGHRL  | C44  | Register  | 64            | RL       | 16                |  |

| LOAD LOGICAL RELATIVE LONG          | LLGFRL | C4E  | Register  | 64            | RL       | 32                |  |

| LOAD LOGICAL HALFWORD RELATIVE LONG | LLHRL  | C42  | Register  | 32            | RL       | 16                |  |

| LOAD LOGICAL HALFWORD RELATIVE LONG | LLGHRL | C46  | Register  | 64            | RL       | 16                |  |

| STORE RELATIVE LONG                 | STRL   | C4F  | Register  | 32            | RL       | 32                |  |

| STORE RELATIVE LONG                 | STGRL  | C4B  | Register  | 64            | RL       | 64                |  |

| STORE HALFWORD RELATIVE LONG        | STHRL  | C47  | Register  | 16            | RL       | 16                |  |

#### **Explanation:**

Operand must be aligned on an integral boundary; otherwise, a specification exception is

recognized!

RL Relative-long operand; 32-bit immediate value, multiplied by two and added to the current

instruction address, provides the storage location of the operand

4<u>5dex</u>

**Note Well!** The original IBM S/360 imposed integral-alignment requirements for various storage operands. For example, a LOAD instruction required that the storage operand be aligned on a fullword boundary; otherwise, a specification exception was recognized. With the advent of the S/370, most of these restrictions were relaxed such that no particular alignment (usually) required.

With the GIEF instructions having relative-long second operands, the alignment restrictions are reinstated. The second operand for each of these instructions must be aligned on an integral boundary corresponding to the operand's size. For example, for LOAD RELATIVE LONG (LGRL), the second operand must be aligned on a doubleword boundary; for LRL, the second operand must be aligned on a fullword boundary; otherwise, a specification exception is recognized. Because the I<sub>2</sub> field designates a number of halfwords, second operands that are 16 bit in length are necessarily aligned on a halfword.

Why – after all these years of alignment emancipation – was such a restriction reintroduced? As we noted in the introduction, a primary goal of GEIF was high performance. The alignment of these operands is necessary to achieve the desired performance.

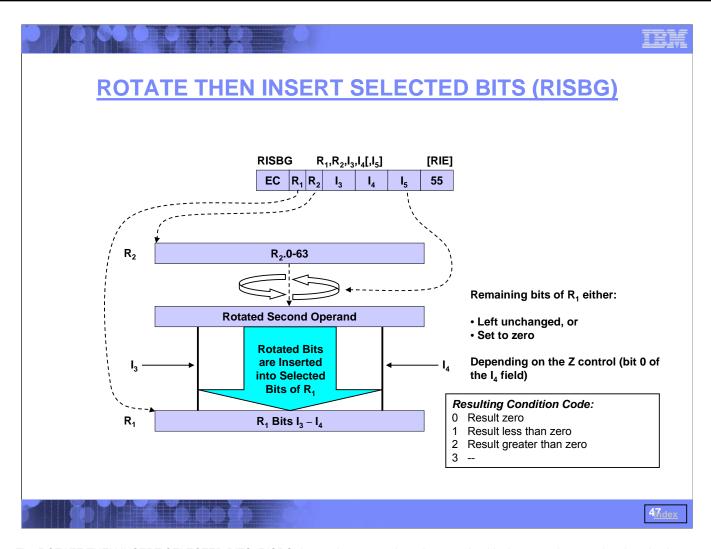

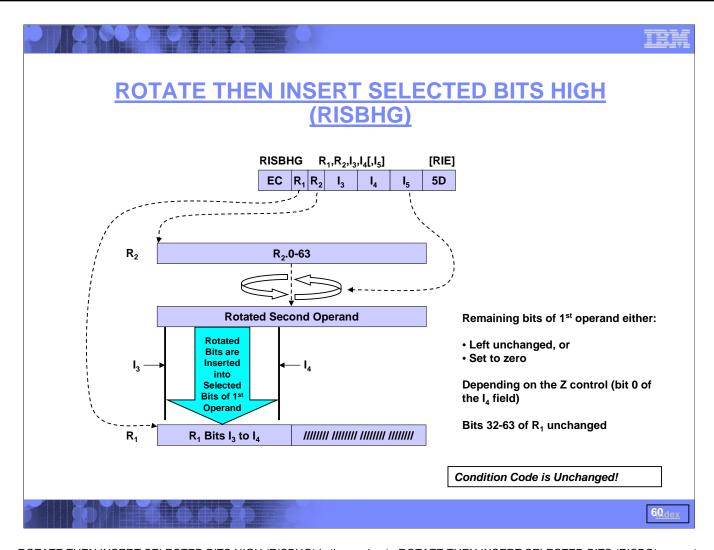

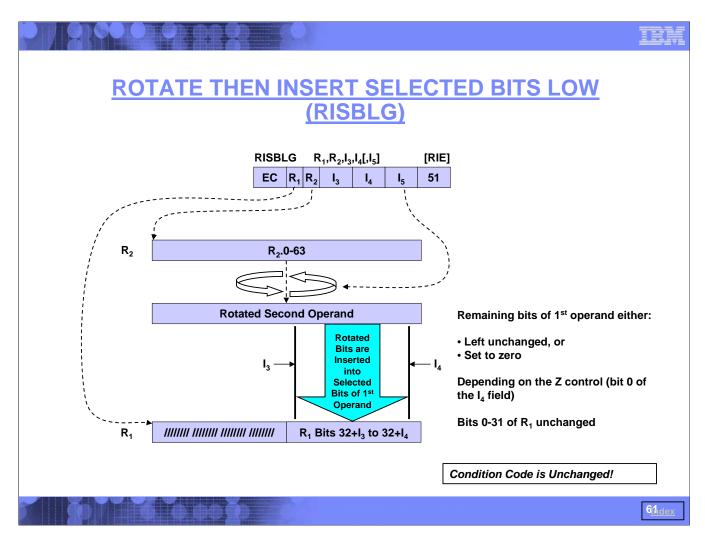

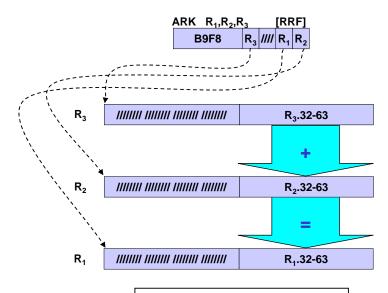

# **General-Instructions Extension Facility: Rotate Then xxx Selected Bits**

| Instruction                            | Mne-  | Ор-  | First Operand |      | Second Opera | nd   |

|----------------------------------------|-------|------|---------------|------|--------------|------|

|                                        | monic | Code | Location      | Size | Location     | Size |

| ROTATE THEN AND SELECTED BITS          | RNSBG | EC54 | Register      | 64   | Register     | V    |

| ROTATE THEN EXCLUSIVE OR SELECTED BITS | RXSBG | EC57 | Register      | 64   | Register     | V    |

| ROTATE THEN INSERT SELECTED BITS       | RISBG | EC55 | Register      | 64   | Register     | V    |

| ROTATE THEN OR SELECTED BITS           | ROSBG | EC56 | Register      | 64   | Register     | V    |

#### **Explanation:**

Variable number of bits processed, based on I<sub>3</sub> and I<sub>4</sub> operands of the instruction.

4<u>6dex</u>

Four instructions perform a rotate-left operation on the second-operand register; bits that rotate out of bit position zero reenter the register at bit position 63. Subsequently, depending on the instruction, one of four operations is performed using selected bits of the rotated value and the first-operand register.

The following slides provide additional details.